PCIe Generations from Leading-Edge to Legacy, Desktop to Data Center

By Kay Annamalai, Senior Marketing Director, Diodes Incorporated

The global appetite for data shows no sign of abating and continues to place pressure on service providers to handle more bits, more quickly. This pressure is felt acutely in large-scale data centers, which are dealing with increasingly bandwidth-hungry trends. Such trends include growth in demand for entertainment streaming, IoT applications, services associated with connected cars and autonomous driving, and enterprise digital transformation with intensive analytics.

Data Centers Driving Interface Evolution

There is an urgent demand for faster data-transfer protocols throughout the infrastructure, including handling the increasing volumes of data arriving over vast numbers of channels, storing and maintaining the data, retrieving and processing the data, and returning the results – with value added – to the client.

The various bodies responsible for today’s networking and interface protocols are working intensively to squeeze the next performance increases from their standards. However, excessive speed mismatches between different points in the network can lead to bottlenecks. The pace of progress needs to be high at the leading edge, but it is also important that the different protocols should move forward at a similar rate.

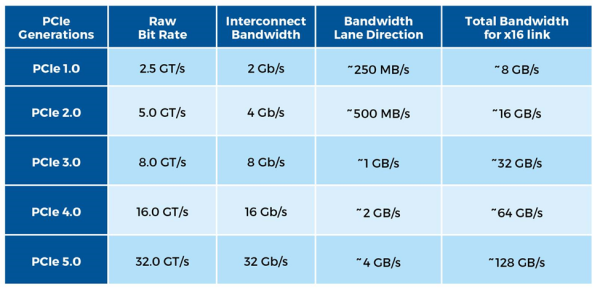

The evolution of PCIexpress® (PCIe®) has approximately kept pace with evolving multi-gigabit Ethernet specifications, driven by the needs of leading data center operators. Operators are in the process of moving from 100Gbit Ethernet to adopt the latest 400Gbit connections throughout their premises. To maximize the gain achieved, newer and faster PCIe generations are needed to connect the data center’s servers with local peripherals, such as storage and AI accelerator cards. The PCIe 4.0 specification was announced in 2017, doubling the bandwidth of the preceding generation. This was followed by the publication of PCIe 5.0 in 2019, raising the transfer speed to 32GT/s to give a total bandwidth of 128GB/s for an x16 link.

Figure 1 summarizes the aggregate speeds of the various PCIe generations. The PCI-SIG is already working on PCIe 6.0 and expects to complete the new specification in 2021. It is likely that PCIe will continue to be the protocol of choice for performance-hungry peripheral communications.

Figure 1. PCIe standards have evolved at a similar pace to multi-gigabit Ethernet.

The Unique Longevity of PCIe Specifications

PCIe 5.0 products are entering the market now. However, there are no expiry dates for the older specifications. Backwards compatibility is a key strength of PCIe that allows the earlier specifications to offer a proven and high-performing solution for opportunities, such as personal computing, gaming, and some enterprise computing and networking applications.

In addition to the devices designed to the latest specifications, designers need highly integrated off-the-shelf PCIe chips that support earlier generations to take advantage of these established and widely accepted standards. Designers can then choose the most suitable option from several PCIe generations to achieve a practicable and affordable solution that delivers outstanding performance. Chip makers, for their part, can continue to leverage their design IP and investment in customer support knowhow associated with each generation of the PCIe standards.

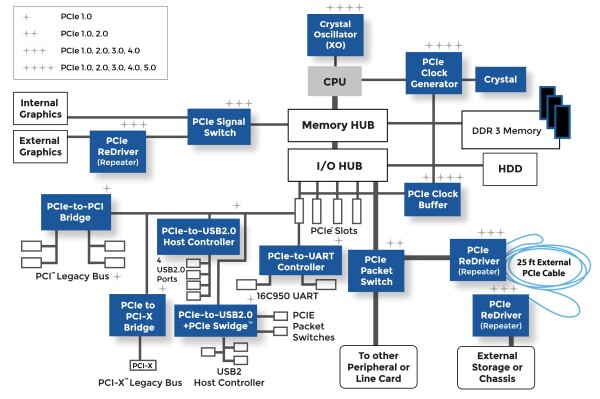

Diodes has a large selection of standard ICs that provide support for PCIe generations 2.0, 3.0, 4.0, and 5.0 (shown in figure 2). Designers can choose from any of these to implement high-performance interfaces for a wide variety of applications.

Figure 2. The Diodes portfolio provides a comprehensive selection for PCIe 1.0, 2.0, 3.0, 4.0, and 5.0.

Flexible Design with Diodes’ PCIe ICs

Bridges and switches, as shown in figure 2, are key components in PCIe architectures and are used for interfacing between host and endpoint devices of various types. A packet bridge typically provides an interface between two layers in the OSI reference model or between two protocols. A bridge can also be used to connect between PCIe and legacy PCI standards, including PCI-X, or to USB ports or a UART bus interface. Packet switches are multiport/multilane devices typically used to expand a single root complex to several ports. Additional lanes are provided for accessing other peer systems, such as a peripheral or line card. Diodes offers packet bridges and switches with various port configurations and translation capabilities.

Moreover, Diodes has combined the functionalities of a PCIe packet switch and PCIe-to-USB2.0 bridge to create the PI7C9X442SL PCI Express-to-USB 2.0 PCIe Swidge™. This innovative device can fan out from one PCIe x1 upstream port, to two x1 downstream and four USB 2.0 ports, allowing access to multiple PCIe and USB devices from the system host processor.

To boost signal integrity in high-speed systems, or wherever signals are required to be driven across a longer connection (such as to an external graphics card or external storage), a PCIe ReDriver™ for PCIe 2.0, PCIe 3.0, and PCIe 4.0 may be used, as shown in figure 2. The ReDriver compensates for transmission-line losses using techniques such as equalization and pre-emphasis, and contains an output driver that introduces minimal latency. The effect is to restore signal margin and minimize jitter, effectively maintaining a low bit-error rate at the receiver. A ReDriver can be easier and more economical to implement than a retimer, which integrates additional functions including clock and data recovery.

In addition, Diodes has a portfolio of passive bidirectional PCIe 2.0, PCIe 3.0, and PCIe 4.0 signal multiplexers/demultiplexers. These can be used to connect a single PCIe lane to multiple lanes, such as for bandwidth expansion for graphics or computation, or to connect a system to a multi-protocol interface.

Diodes also has timing ICs for all PCIe generations, indicated by the crystal oscillator, clock generator, and clock buffer functions shown in the diagram. Diodes’ PCIe clock generators can produce a specific clock signal frequency with very low output jitter suitable for PCIe applications and other system clocks that demand similar performance. The clock buffer takes the clock-generator reference signal and produces multiple outputs to distribute across the PCB. Various configurations are available, leveraging Diodes’ proprietary PLL design that minimizes jitter to satisfy the applicable PCIe specification. Among the devices available, Diodes’ 1.8V PI6CG18xxx clock generators and 1.5V PI6CG15xxx buffers are PCIe 4.0 ICs available in 2-, 4-, and 8-channel configurations. Their integrated features save four external resistors per output, reducing the bill of materials by 32 components for an 8-channel implementation.

Conclusion

The PCIe standards are at the forefront of development, enabling the high-bandwidth interconnects demanded by leading-edge hyper-scale data centers. In addition to the high speed of the latest generation, which is closely matched to the fastest multi-gigabit Ethernet specifications, the longevity of older standards and assured backwards compatibility between the generations enable designers to create practical, affordable, and high-performing solutions for consumer, desktop, and industrial purposes. The support of a broad portfolio of PCIe chips that cover multiple generations of the standard – such as the Diodes PCIe portfolio of timing chips, drivers, ReDrivers, switches, and bridges – is an essential ingredient for success.

PCIexpress®, PCIe®, PCI-SIG® and PCITM are trademarks or registered trademarks and/or service marks of PCI-SIG Corporation. All other trademarks are the property of their respective owners.

ReDriver™ is a trademark of Diodes Incorporated.