| Document Date<br>Feb 21, 2014 |  | DOCUMENT-REV 1.0 | PAGE<br>Page 1 of 1 |

|-------------------------------|--|------------------|---------------------|

|-------------------------------|--|------------------|---------------------|

# PI6C485311 Application Note

#### 1. Introduction

The PI6C485311 is one universal differential input (LVPECL, LVDS, HCSL, and CML) and two LVPECL differential output 8 pin IC. It fits for Datacom, Netcom, and Telecom application designs.

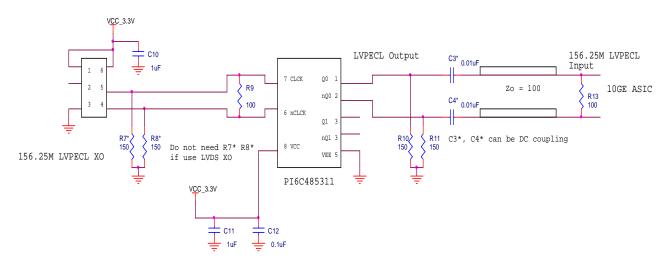

## 2. Application Reference Circuit

#### Note:

- 1) Put 0.1uf decoupling cap. on each VDD pin comp. side; 1uf can be put on the bottom side

- 2) Leave un-used Qx and nQx output just open in NC

- 3) LVPECL needs 150 pull-down to drive RX equiv. 100 diff. load, LVDS output does not need 150 pull-down

### 3. Differential Input

This device has no internal 50 termination and can not accept AC direct drive \_\_can not accept negative signal drive, so external termination or DC bias termination must be applied when use AC drive like CML, except when use HCSL signal drive that do not need RX 50 ohm termination.

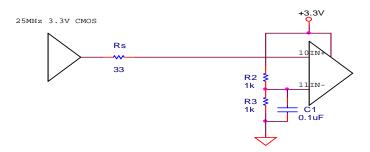

The differential input can accept single CMOS clock drive too as the following diagram:

#### 4. LVPECL Differential Output PCB

- i) 150 ohm pull-down would be put close to clock output side (<0.250mil) with symmetrical position in one pair

- ii) It is better not to share 150 ohm pull-down GND via with adjacent pairs' 150 ohm's GND via

- iii) Termination scheme is on the reference schematic type in either AC or DC coupling