#### **DESCRIPTION**

The AP63300Q and AP63301Q are 3A, synchronous buck converters each with a wide input voltage range of 3.8V to 32V. The devices fully integrate a 75m $\Omega$  high-side power MOSFET and a 40m $\Omega$  low-side power MOSFET to provide higherficiency step-down DC-DC conversion.

The AP63300Q and AP63301Q are easily used by minimizing the external component count due to their adoption of peak current mode control along with their integrated loop compensation network.

The AP63300Q and AP63301Q are optimized for Electromagnetic Interference (EMI) reduction. The device has a proprietary gate driver scheme to resist switching node ringing without sacrificing MOSFET turn-on and turn-off times, reducing high-frequency radiated EMI noise caused by MOSFET switching. AP63300Q also features Frequency Spread Spectrum (FSS) with a switching frequency jitter of ±6%, reducing EMI by not allowing emitted energy to stay in any one frequency for a significant period of time.

The devices are available in the TSOT26 package.

### **FEATURES**

- VIN 3.8V to 32V

- 3A Continuous Output Current

- 0.8V ± 1% Reference Voltage

- 22µA Ultralow Quiescent Current (Pulse Frequency Modulation)

- 500kHz Switching Frequency

- Supports Pulse Frequency Modulation (PFM)

- o AP63300Q

- Up to 88% Efficiency at 5mA Light Load

- Pulse Width Modulation (PWM) Regardless of Output Load

- o AP63301Q

- Proprietary Gate Driver Design for Best EMI Reduction

- Frequency Spread Spectrum (FSS) to Reduce EMI

- o AP63300Q

- Low-Dropout (LDO) Mode

- Precision Enable Threshold to Adjust UVLO

- Protection Circuitry

- Undervoltage Lockout (UVLO)

- Output Overvoltage Protection (OVP)

- Cycle-by-Cycle Peak Current Limit

- Thermal Shutdown

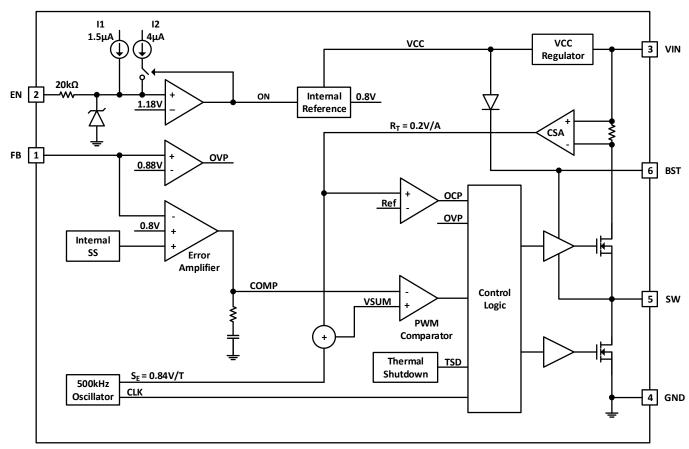

# **FUNCTIONAL BLOCK**

Figure 1. Functional Block Diagram

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                      | Parameter Rating        |                                       | Unit |

|-----------------------------|-------------------------|---------------------------------------|------|

| VIN                         | Supply Pin Voltage      | -0.3 to +35.0 (DC)                    | V    |

|                             | Supply Fill Voltage     | -0.3 to +40.0 (400ms)                 |      |

| VFB                         | Feedback Voltage        | Feedback Voltage -0.3V to +6.0        |      |

| VEN                         | Enable/UVLO Pin Voltage | Enable/UVLO Pin Voltage -0.3 to +35.0 |      |

| VSW                         | Switch Nada Valtage     | -0.3 to VIN + 0.3 (DC)                | V    |

|                             | Switch Node Voltage     | -2.5 to VIN + 2.0 (20ns)              | V    |

| VBST                        | Bootstrap Pin Voltage   | VSW - 0.3 to VSW + 6.0                | V    |

| TST                         | Storage Temperature     | -65 to +150                           | °C   |

| TJ                          | Junction Temperature    | +160                                  | °C   |

| TL                          | Lead Temperature        | +260                                  | °C   |

| ESD Susceptibility (Note 5) |                         |                                       |      |

| HBM                         | Human Body Mode         | 2000                                  | V    |

| CDM                         | Charged Device Model    | 1000                                  | V    |

### RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                            | Min | Max  | Unit |

|--------|--------------------------------------|-----|------|------|

| VIN    | Supply Voltage                       | 3.8 | 32   | V    |

| VOUT   | Output Voltage                       | 0.8 | 31   | V    |

| TA     | Operating Ambient Temperature Range  | -40 | +125 | °C   |

| TJ     | Operating Junction Temperature Range | -40 | +150 | °C   |

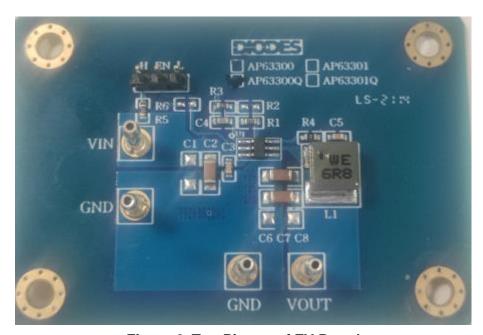

### **EVALUATION BOARD**

Figure 2. Top Picture of EV Board

# **QUICK START GUIDE**

The AP63300Q/1Q-EVM has a simple layout and allows access to the appropriate signals through test points. To evaluate the performance of the AP63300Q/1Q, follow the procedure below:

- 1. For evaluation board configured at V<sub>OUT</sub>=5V, connect a power supply to the input terminals V<sub>IN</sub> and GND. Set V<sub>IN</sub> to 12V.

- 2. Connect the positive terminal of the electronic load to Vout and negative terminal to GND.

- 3. For Enable, place a jumper to "H" position to enable IC. Jump to "L" position to disable IC.

- 4. The evaluation board should now power up with a 5V output voltage.

- 5. Check for the proper output voltage of 5V (±1%) at the output terminals VouT and GND. Measurement can also be done with a multimeter with the positive and negative leads between VouT and GND.

- 6. Set the load to 3A through the electronic load. Check for the stable operation of the SW signal on the oscilloscope. Measure the switching frequency.

### **MEASUREMENT/PERFORMANCE GUIDELINES:**

- When measuring the output voltage ripple, maintain the shortest possible ground lengths on the oscilloscope probe. Long ground leads can erroneously inject high frequency noise into the measured ripple.

- 2) For efficiency measurements, connect an ammeter in series with the input supply to measure the input current. Connect an electronic load to the output for output current.

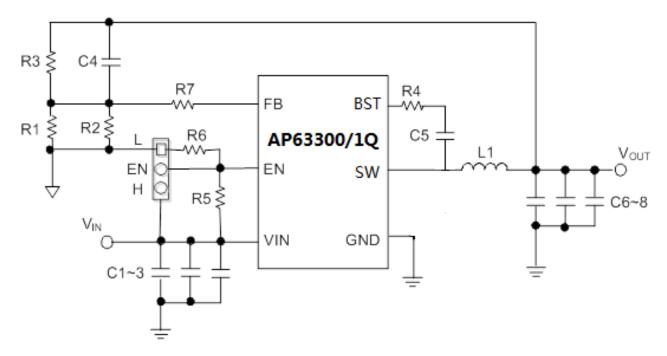

# Setting the Output Voltage of AP63300Q/1Q

1) Setting the output voltage

The AP63300Q/1Q features external programmable output voltage by using a resistor divider network R3 and R1 as shown in the typical application circuit. The output voltage is calculated as below,

$$V_{OUT} = 0.8 \times \left(\frac{R_1 + R_3}{R_1}\right)$$

First, select a value for R1 according to the value recommended in the table 1. Then, R3 is determined. The output voltage is given by Table 1 for reference. For accurate output voltage, 1% tolerance is required.

2) Output feed-forward capacitor selection

The AP63300Q/1Q has the internal integrated loop compensation as shown in the function block diagram. The compensation network includes an 18k resistor and a 7.6nF capacitor. Usually, the type II compensation network has a phase margin between 60 and 90 degree. However, if the output capacitor has ultra-low ESR, the converter results in low phase margin. To increase the converter phase margin, a feed-forward cap C4 is used to boost the phase margin at the converter cross-over

frequency  $f_{\it C}$  . The feed-forward capacitor is given by Table 1 for reference. The feed-forward capacitor is calculated as below,

$$C_{ff} = \frac{1}{2\pi \times f_{C} \times R_{3}}$$

Table 1. Resistor selection for output voltage setting

| Vo   | R3      | R1    | C4     | C6-C8  |

|------|---------|-------|--------|--------|

| 1.8V | 77.5 KΩ | 62 KΩ | 100pF  | 22uFx2 |

| 2.5V | 131 ΚΩ  | 62 KΩ | 100pF  | 22uFx2 |

| 3.3V | 182 ΚΩ  | 62 KΩ | 100 pF | 22uFx2 |

| 5V   | 157 KΩ  | 30 KΩ | 100 pF | 22uFx2 |

| 12V  | 249 ΚΩ  | 18 ΚΩ | 56 pF  | 22uFx4 |

# **EXTERNAL COMPONENT SELECTION:**

- 1) Input & output Capacitors (Cin, Cout)

- (1) For lower output ripple, low ESR is required.

- (2) Low leakage current needed, multiple capacitor parallel connection.

- (3) The Cin and Cout capacitances are greater than 10µF and 44µF respective.

- 2) Bootstrap Voltage Regulator

- (1) An external 0.1µF ceramic capacitor is required as bootstrap capacitor between BST and SW pin to work as high side power MOSFET gate driver.

- 3) Inductor (L)

- (1) Low DCR for good efficiency

- (2) Inductance saturate current must higher than the output current

- (3) The recommended inductance is shown in the table 2 below.

# **EVALUATION BOARD SCHEMATIC**

**Figure 3. Typical Application Circuit**

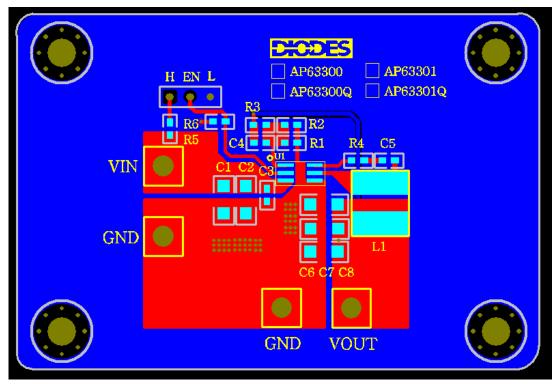

# **PCB TOP LAYOUT**

Figure 4. AP63300Q/1Q-EVM - Top Layer

# **PCB BOTTOM LAYOUT**

Figure 5. AP63300Q/1Q -EVM - Bottom Layer

# BILL OF MATERIALS for AP63300Q/1Q-EVM

| Item    | Value | Туре                 | Rating | Description      | Description                  |

|---------|-------|----------------------|--------|------------------|------------------------------|

| C2      | 10μF  | X7R,<br>Ceramic/1206 | 35V    | Input CAP        | TDK<br>CGA5L1X7R1V106K160AC  |

| C3      | 0.1µF | X8R,<br>Ceramic/0603 | 50V    | Input CAP        | TDK<br>CGA3E3X8R1H104K080AB  |

| C4      | 100pF | C0G,<br>Ceramic/0603 | 50V    | Feedback CAP     | TDK<br>CGA3E2C0G1H101J080AA  |

| C5      | 0.1µF | X8R,<br>Ceramic/0603 | 50V    | Bootstrap CAP    | TDK<br>CGA3E3X8R1H104K080AB  |

| C6 & C7 | 22µF  | X7R,<br>Ceramic/1206 | 10V    | Output CAP       | TDK<br>CGA5L1X7S1A226M160AC  |

| L1      | 6.8µH | 6060                 | 6.5A   | Inductor         | Würth PART<br>744 393 690 68 |

| R1      | 30K   | 0603                 | 1%     | Voltage set BEC* |                              |

| R3      | 162K  | 0603                 | 1%     | Voltage set RES* |                              |

| R4      | 0     | 0603                 | 1%     | Bootstrap RES    |                              |

| R5      | 100K  | 0603                 | 1%     | EN pull high RES |                              |

| U1      |       | AP63300Q/1Q          |        | TSOT23-6         | Diodes BCD                   |

<sup>\*</sup>Note: The present value of R3/R1 are based on Vout=5.0V

Table 2

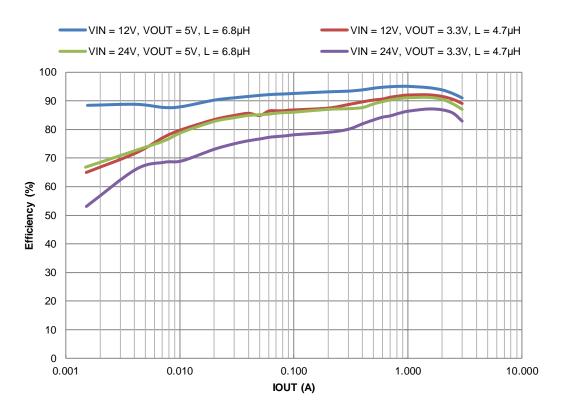

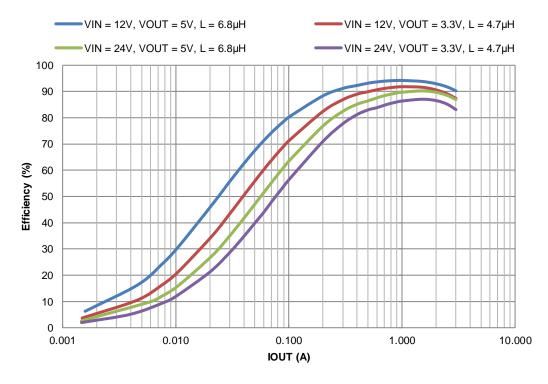

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 6. AP63300Q Efficiency vs. Output Current

Figure 7. AP63301Q Efficiency vs. Output Current

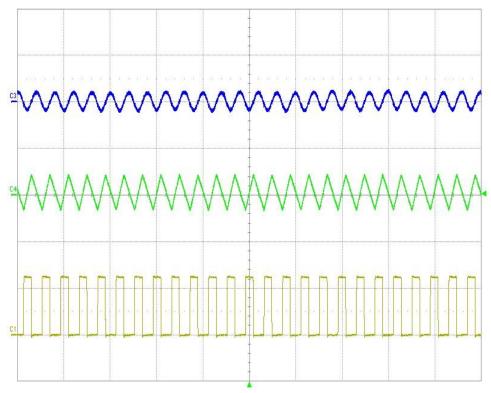

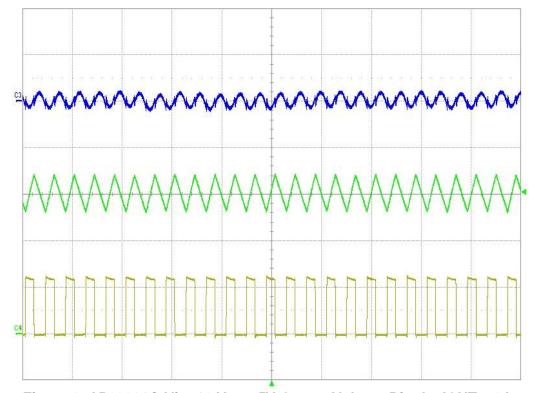

Figure 8. AP63301Q Vin=12 Vout=5V Output Voltage Ripple, IOUT = 50mA

Figure 9. AP63301Q Vin=12 Vout=5V Output Voltage Ripple, IOUT = 3A

# AP63300Q/1Q-EVM

# 3.8V TO 32V INPUT, 3A LOW IQ SYNCHRONOUS BUCK WITH ENCHANCED EMI REDUCTION

#### IMPORTANT NOTICE

- 1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (<a href="https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/">https://www.diodes.com/about/company/terms-and-conditions-of-sales/</a>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- 9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners.

© 2023 Diodes Incorporated. All Rights Reserved.

www.diodes.com