# **PART OBSOLETE - DISCONTINUED**

# PI3VDP411LSA

# **Dual Mode DisplayPort™ to DVI/HDMI™ Electrical bridge (Level Shifter)**

#### **Features**

- → Converts low-swing AC coupled differential input to HDMI™ rev 1.3 compliant open-drain current steering Rx terminated differential output

- → HDMI Level shifting operation up to 2.5Gbps per lane (250MHz pixel clock)

- → Integrated 50-ohm termination resistors for AC-coupled differential inputs.

- → Provide Output Squelch function to turn off TMDS common mode output buffer when TMDS clock is not present

- → Enable/Disable feature to turn off TMDS outputs to enter low-power state.

- → Output slew rate control on TMDS outputs to minimize EMI

- → Integrated Active / Passive DDC level shifters (3.3V source to 5V sink)

- → Transparent operation: no re-timing or configuration required

- → Level shifter for HPD signal from HDMI/DVI connector

- → Integrated pull-down on HPD\_sink input guarantees "input low" when no display is plugged in

- → 3.3V Power supply required

- → TMDS output enable control

- → ESD protection on all I/O pins

- 4kV HBM

- □ ±8kV contact ESD protection on the following pins

- $\rightarrow$  OUT\_Dx±

- → SDA\_SINK, SCL\_SINK

- → HPD SINK

- → Packaging (Pb-free & Green available):

- □ 48 TQFN, 7mm × 7mm (ZBE)

## Description

Pericom Semiconductor's PI3VDP411LSA provides the ability to use a Dual-mode DisplayPort™ transmitter in HDMI™ mode. This flexibility provides the user a choice of how to connect to their favorite display. All signal paths accept AC coupled video signals. The PI3VDP411LSA converts this AC coupled signal into an HDMI rev 1.3 compliant signal with proper signal swing. This conversion is automatic and transparent to the user.

Output squelch function is provided for each channel. When output channel is enable (OE#=0) and operating, that TMDS pixel clock input signal determines whether the output is enabled. When no TMDS pixel clock is present, TMDS output channel will be disabled.

The PI3VDP411LSA supports up to 2.5Gbps, which provides 12-bits of color depth per channel, as indicated in HDMI rev 1.3.

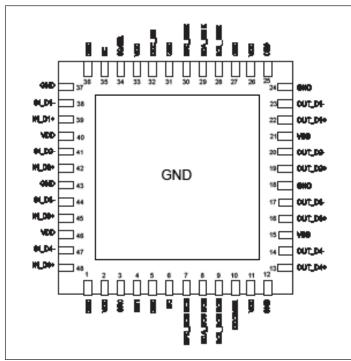

## Pin Configuration (48-Pin TQFN)

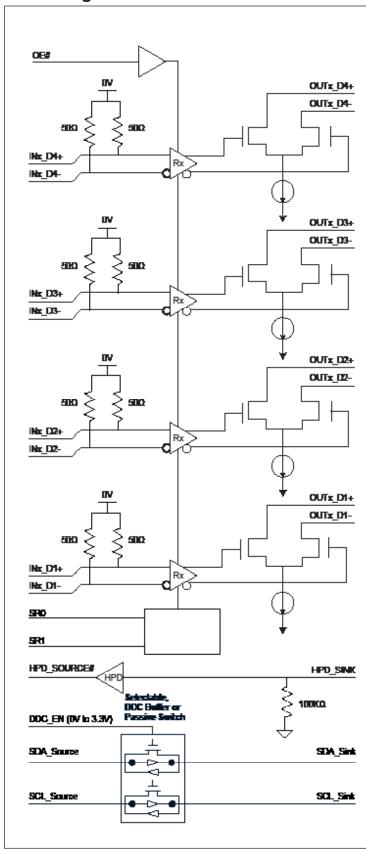

## **Block Diagram**

## **Pin Description**

| Pin                                     | Name       | I/O Type | Descriptions                                                                        |                    |          |                                                                                                       |  |                                                                             |  |

|-----------------------------------------|------------|----------|-------------------------------------------------------------------------------------|--------------------|----------|-------------------------------------------------------------------------------------------------------|--|-----------------------------------------------------------------------------|--|

| 1, 5, 12, 18, 24,<br>27, 31, 36, 37, 43 | GND        | POWER    | GROUND                                                                              | GROUND             |          |                                                                                                       |  |                                                                             |  |

| 2, 11, 15, 21, 26, 33, 40, 46           | $V_{DD}$   | POWER    | POWER, 3.3V                                                                         | POWER, 3.3V ±10%   |          |                                                                                                       |  |                                                                             |  |

| 3, 4                                    | SR0, SR1   | I        |                                                                                     |                    |          | ble connections to SRx pin are: resistor to 3.3V or 0K $\Omega$ pull-LOW)                             |  |                                                                             |  |

| 6, 35                                   | NC         | О        | No Connect                                                                          |                    |          |                                                                                                       |  |                                                                             |  |

| 7                                       | HPD_SOURCE | 0        |                                                                                     |                    |          | (nominal) output signal. HPD_Sink input can be as Source will output no higher than 3.3V.             |  |                                                                             |  |

|                                         |            |          | 3.3V DDC Da                                                                         | ata I/O            | . Pulled | l up by external termination to 3.3V.                                                                 |  |                                                                             |  |

|                                         |            |          | DDC_EN                                                                              | DDC                | BSEL     | DDC level shifter type                                                                                |  |                                                                             |  |

|                                         |            |          | Low                                                                                 | X                  |          | DISABLE DDC level shifter                                                                             |  |                                                                             |  |

|                                         |            |          |                                                                                     |                    |          | Passive level shifter ENABLE                                                                          |  |                                                                             |  |

| 8                                       | SDA_SOURCE | I/O      | High                                                                                | High Low High High |          | Low                                                                                                   |  | Connected to SDA_SINK through voltage-<br>limiting integrated NMOS passgate |  |

|                                         |            |          |                                                                                     |                    |          |                                                                                                       |  | Active level shifter ENABLE                                                 |  |

|                                         |            |          | High                                                                                |                    |          | Connected to SDA_SINK through bi-direction buffer                                                     |  |                                                                             |  |

|                                         |            |          | 3.3V DDC Data I/O. Pulled                                                           |                    | . Pulled | l up by external termination to 3.3V.                                                                 |  |                                                                             |  |

|                                         |            |          | DDC_EN DDC                                                                          |                    | BSEL     | DDC level shifter type                                                                                |  |                                                                             |  |

|                                         |            |          | Low                                                                                 | X                  |          | DISABLE DDC level shifter                                                                             |  |                                                                             |  |

| 9                                       | SCL_SOURCE | I/O      | High                                                                                | Low                |          | Passive level shifter ENABLE Connected to SCL_SINK through voltage- limiting integrated NMOS passgate |  |                                                                             |  |

|                                         |            |          | High                                                                                | High               |          | Active level shifter ENABLE Connected to SCL_SINK through bi-direction buffer                         |  |                                                                             |  |

|                                         |            |          | Active DDC l                                                                        | evel sh            | ifter en | able pin. (internal 200KΩ pull-LOW)                                                                   |  |                                                                             |  |

|                                         |            |          | DDCBSEL                                                                             |                    | DDC path |                                                                                                       |  |                                                                             |  |

| 10                                      | DDCBSEL    | I        | Low (0V)                                                                            |                    | Passiv   | re DDC level shifter                                                                                  |  |                                                                             |  |

|                                         |            |          | High (3.3V)                                                                         |                    | Active   | e DDC level shifter                                                                                   |  |                                                                             |  |

| 13                                      | OUT_D4+    | О        | HDMI 1.3 compliant TMDS output. OUT_D4+ makes a differential out signal with OUT_D4 |                    |          | S output. OUT_D4+ makes a differential output                                                         |  |                                                                             |  |

| 14                                      | OUT_D4-    | О        | HDMI 1.3 cor                                                                        |                    |          | S output. OUT_D4- makes a differential output                                                         |  |                                                                             |  |

| 16                                      | OUT_D3+    | О        | HDMI 1.3 cor<br>signal with O                                                       | -                  |          | S output. OUT_D3+ makes a differential output                                                         |  |                                                                             |  |

| 17                                      | OUT_D3-    | О        | HDMI 1.3 cos<br>signal with O                                                       |                    |          | S output. OUT_D3- makes a differential output                                                         |  |                                                                             |  |

| Pin | Name       | I/O Type | Descriptions                                                                                                                                                                                                                             |                                                                                        |                                                                                                  |                                                                                                         |                   |  |

|-----|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|--|

| 19  | OUT_D2+    | О        |                                                                                                                                                                                                                                          | HDMI 1.3 compliant TMDS output. OUT_D2+ makes a differential output signal with OUT_D2 |                                                                                                  |                                                                                                         |                   |  |

| 20  | OUT_D2-    | О        | HDMI 1.3 co                                                                                                                                                                                                                              |                                                                                        | OS output                                                                                        | . OUT_D2- makes a diffe                                                                                 | erential output   |  |

| 22  | OUT_D1+    | О        | HDMI 1.3 co                                                                                                                                                                                                                              |                                                                                        | OS output                                                                                        | . OUT_D1+ makes a diff                                                                                  | erential output   |  |

| 23  | OUT_D1-    | О        | HDMI 1.3 co                                                                                                                                                                                                                              |                                                                                        | OS output                                                                                        | . OUT_D1- makes a diffe                                                                                 | erential output   |  |

|     |            |          | Enable for le                                                                                                                                                                                                                            | vel shifter pat                                                                        | h.                                                                                               |                                                                                                         |                   |  |

|     |            |          | OE#                                                                                                                                                                                                                                      | IN_D Teri                                                                              | mination                                                                                         | OUT_D Outputs                                                                                           |                   |  |

| 25  | OE#        | I        | 1                                                                                                                                                                                                                                        | > 100KΩ                                                                                |                                                                                                  | High-Z                                                                                                  |                   |  |

|     |            |          | 0                                                                                                                                                                                                                                        | 50Ω                                                                                    |                                                                                                  | Active                                                                                                  |                   |  |

|     |            |          | 5V DDC Clo                                                                                                                                                                                                                               | ock I/O. Pulled                                                                        | d up by ex                                                                                       | sternal termination to 5V                                                                               | •                 |  |

|     |            |          | DDC_EN                                                                                                                                                                                                                                   | DDCBSEL                                                                                | DDC le                                                                                           | evel shifter type                                                                                       |                   |  |

|     | 8 SCL_SINK |          | Low                                                                                                                                                                                                                                      | X                                                                                      | DISAB                                                                                            | DISABLE DDC level shifter                                                                               |                   |  |

| 28  |            | I/O      | High                                                                                                                                                                                                                                     | Low                                                                                    | Conne                                                                                            | Passive level shifter ENABLE Connected to SCL_SOURCE through voltage- limiting integrated NMOS passgate |                   |  |

|     |            |          | High                                                                                                                                                                                                                                     | High                                                                                   | Conne                                                                                            | Active level shifter ENABLE<br>Connected to SCL_SOURCE through bi-<br>direction buffer                  |                   |  |

|     |            |          | 5V DDC Da                                                                                                                                                                                                                                | ta I/O. Pulled                                                                         | up by ext                                                                                        | ernal termination to 5V.                                                                                |                   |  |

|     |            |          | DDC_EN                                                                                                                                                                                                                                   | DDCBSEL                                                                                | DDC le                                                                                           | evel shifter type                                                                                       |                   |  |

|     |            |          | Low                                                                                                                                                                                                                                      | X                                                                                      | DISAB                                                                                            | LE DDC level shifter                                                                                    |                   |  |

| 29  | SDA_SINK   | I/O      | High                                                                                                                                                                                                                                     | Low                                                                                    | Passive level shifter ENABLE Connected to SDA_SOURCE through v limiting integrated NMOS passgate |                                                                                                         |                   |  |

|     |            |          | High                                                                                                                                                                                                                                     | High                                                                                   | Conne                                                                                            | Active level shifter ENABLE Connected to SDA_SOURCE through bi- direction buffer                        |                   |  |

| 30  | HPD_SINK   | I        | Low Frequency, 0V to 5V (nominal) input signal. This signal comes from the TMDS connector. Voltage High indicates "plugged" state; voltage low indicates "unplugged". HPD_SINK is pulled down by an integrated 100K ohm puller resistor. |                                                                                        |                                                                                                  |                                                                                                         | oltage low indica |  |

|     |            |          | Enables DD                                                                                                                                                                                                                               | C level shifter                                                                        | path                                                                                             |                                                                                                         |                   |  |

|     |            |          | DDC_EN                                                                                                                                                                                                                                   |                                                                                        |                                                                                                  | Passgate                                                                                                |                   |  |

| 32  | DDC_EN     | I        | Low (0V)                                                                                                                                                                                                                                 |                                                                                        |                                                                                                  | Disable                                                                                                 |                   |  |

|     |            |          | High (3.3V)                                                                                                                                                                                                                              | ١                                                                                      |                                                                                                  | Enable                                                                                                  |                   |  |

# $Dual\ Mode\ DisplayPort^{"}\ to\ DVI/HDMI^{"}\ Electrical\ bridge\ (Level\ Shifter)$

| Pin | Name   | I/O Type | Descriptions                                                                           |  |  |  |  |

|-----|--------|----------|----------------------------------------------------------------------------------------|--|--|--|--|

|     |        |          | TMDS clock detection setting                                                           |  |  |  |  |

|     |        |          | Pulled up by external termination to 3.3V or short to GND.                             |  |  |  |  |

|     |        |          | SQSEL   Clock Monitor Pin                                                              |  |  |  |  |

| 34  | SQSEL  | I        | Device monitor HDMI pixel clock on Pin38/39 (Channel IN_D1±)                           |  |  |  |  |

|     |        |          | Device monitor DVI pixel clock on Pin 47/48 (Channel IN_D4±)                           |  |  |  |  |

| 38  | IN_D1- | I        | Low-swing diff input from DP Tx outputs. IN_D1- makes a differential pair with IN_D1+. |  |  |  |  |

| 39  | IN_D1+ | I        | Low-swing diff input from DP Tx outputs. IN_D1+ makes a differential pair with IN_D1   |  |  |  |  |

| 41  | IN_D2- | I        | Low-swing diff input from DP Tx outputs. IN_D2- makes a differential pair with IN_D2+. |  |  |  |  |

| 42  | IN_D2+ | I        | Low-swing diff input from DP Tx outputs. IN_D2+ makes a differential pair with IN_D2   |  |  |  |  |

| 44  | IN_D3- | I        | Low-swing diff input from DP Tx outputs. IN_D3- makes a differential pair with IN_D3+. |  |  |  |  |

| 45  | IN_D3+ | I        | Low-swing diff input from DP Tx outputs. IN_D3+ makes a differential pair with IN_D3   |  |  |  |  |

| 47  | IN_D4- | I        | Low-swing diff input from DP Tx outputs. IN_D4- makes a differential pair with IN_D4+. |  |  |  |  |

| 48  | IN_D4+ | I        | Low-swing diff input from DP Tx outputs. IN_D4+ makes a differential pair with IN_D4   |  |  |  |  |

### Truth Table (Slew Rate control function)

| SR1 | SR0 | Rise/Fall Time (Typ) |

|-----|-----|----------------------|

| 1   | 1   | 140ps                |

| 1   | 0   | 130ps                |

| 0   | 1   | 120ps                |

| 0   | 0   | 110ps                |

# **Test Setup Condition**

$V_{\rm DD}$  = 3.3V, Ambient temperature 25°C

Rise/Fall time is from 20% to 80% on Rising/Falling edge

Date rate: 620 Mbps

Input: 1V differential peak-to-peak clock pattern

Equalization: 3dB

# **Table 1: OE Pin Description**

| OE#                       | Device State                                                                                                                                                                                                                                                               | Comments                                                                                                                                                                                                                                                                   |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asserted (low voltage)    | Differential input buffers and output buffers enabled. Input impedance = $50\Omega$                                                                                                                                                                                        | Normal functioning state for IN_D to OUT_D level shifting function.                                                                                                                                                                                                        |

| Unasserted (high voltage) | Low-power state.  Differential input buffers and termination are disabled. Differential inputs are in a high impedance state.  OUT_D level-shifting outputs are disabled. OUT_D level-shifting outputs are in high impedance state. Internal bias currents are turned off. | Intended for lowest power condition when:  "No display is plugged in or "The level shifted data path is disabled HPD_SINK input and HPD_SOURCE output are not affected by OE# SCL_ SOURCE, SCL_SINK, SDA_SOURCE and SDA_SINK signals and functions are not affected by OE# |

### Absolute Maximum Ratings (Over operating free-air temperature range)

| Item                               | Rating                         |

|------------------------------------|--------------------------------|

| Supply Voltage to Ground Potential | 5.5V                           |

| All Inputs and Outputs             | -0.5V to V <sub>DD</sub> +0.5V |

| Ambient Operating Temperature      | -40 to +85°C                   |

| Storage Temperature                | -65 to +150°C                  |

| Junction Temperature               | 150°C                          |

| Soldering Temperature              | 260°C                          |

Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

### **Electrical Characteristics**

**Table: Power Supplies and Temperature Range**

| Symbol                  | Parameter                                       | Min | Тур | Max | Units       | Comments   |

|-------------------------|-------------------------------------------------|-----|-----|-----|-------------|------------|

| $V_{\mathrm{DD}}$       | 3.3V Power supply                               | 3.0 | 3.3 | 3.6 | V           |            |

| Icc                     | Max Current                                     |     |     | 100 | mA          |            |

| I <sub>CC_squelch</sub> | Supply Current when no TMDS clock present       |     | 8   |     | mA          |            |

| $I_{CCQ}$               | Standby Current                                 |     |     | 2   | mA          | OE# = HIGH |

| T <sub>CASE</sub>       | Case temperature range for operation with spec. | -40 |     | 85  | Celsius (°) |            |

| Table: Differ          | Table: Differential Input Characteristics for IN_Dx signals |       |     |       |       |                                                                                                                                                             |  |  |  |

|------------------------|-------------------------------------------------------------|-------|-----|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                 | Parameter                                                   | Min   | Тур | Max   | Units | Comments                                                                                                                                                    |  |  |  |

| $T_{ m bit}$           | UI, Unit Interval                                           | 360   |     |       | ps    | $T_{bit}$ is determined by the display mode. Nominal bit rate ranges from 250Mbps to 2.5Gbps per lane. Nominal Tbit at 2.5 Gbps = 400 ps. 360ps = 400ps-10% |  |  |  |

| V <sub>RX_DIFF</sub>   | Input Differential Voltage Level                            | 0.175 |     | 1.200 | V     | See note 1 below                                                                                                                                            |  |  |  |

| T <sub>RX_EYE</sub>    | Minimum Eye Width at IN_D input pair                        | 0.8   |     |       | Tbit  |                                                                                                                                                             |  |  |  |

| V <sub>CM-ACp-p</sub>  | AC Peak Common<br>Mode Input Voltage                        |       |     | 100   | mV    | See note 2 below                                                                                                                                            |  |  |  |

| Z <sub>RX_DC</sub>     |                                                             | 40    | 50  | 60    | Ω     | Required IN_D+ as well as IN_D- DC impedance (50 ±20% tolerance).                                                                                           |  |  |  |

| Z <sub>RX-Bias</sub>   |                                                             | 0     |     | 2.0   | V     | Intended to limit power-up stress on chipset's PCIE output buffers.                                                                                         |  |  |  |

| Z <sub>RX_HIGH-Z</sub> |                                                             | 100   |     |       | kΩ    | Differential inputs must be in a high impedance state when OE# is HIGH.                                                                                     |  |  |  |

<sup>1.</sup>  $V_{RX-DIFF} = 2x|V_{RX-D-}V_{RX-D-}|$  Applies to IN\_Dx signals

$V_{RX-CM-DC} = DC(avg)$  of  $|V_{RX-D+} + V_{RX-D-}|/2$

$V_{CM\text{-}AC\text{-}p\text{-}p}$  includes all frequencies above 30 kHz.

#### **TMDS Outputs**

The level shifter's TMDS outputs are required to meet HDMI 1.3 specifications.

The HDMI 1.3 Specification is assumed to be the correct reference in instances where this document conflicts with the HDMI 1.3 specification.

<sup>2.</sup>  $V_{CM-AC-p-p} = |V_{RX-D} - V_{RX-D}|/2 - V_{RX-CM-DC}$

#### Dual Mode DisplayPort™ to DVI/HDMI™ Electrical bridge (Level Shifter)

Table 2: Differential Output Characteristics for TMDS\_OUT signals **Symbol Parameter** Min Max Units **Comments** Typ V<sub>DD</sub> is the DC termination voltage Single-ended high V  $V_{H}$  $V_{DD}$ -10mV V<sub>DD</sub>+10mV in the HDMI or DVI Sink.  $V_{DD}$  is  $V_{DD}$ level output voltage nominally 3.3V Single-ended low level The open-drain output pulls down V  $V_{L}$  $V_{DD}$ -600mV  $V_{DD}$ -500mV  $V_{DD}$ -400mV output voltage from V<sub>DD</sub>. Single ended output Swing down from TMDS termina-425 500 600 mV **V**<sub>SWING</sub> swing voltage tion voltage  $(3.3V \pm 10\%)$ Measured with TMDS outputs Single-ended current 50  $I_{OFF}$ μΑ pulled up to  $V_{DD}$  Max \_(3.6V) in high-Z state through  $50\Omega$  resistors. This differential skew budget is in addition to the skew presented be-Intra-pair differential 30 tween D+ and D- paired input pins. ps T<sub>SKEW-INTRA</sub> skew HDMI revision 1.3 source allowable intrapair skew is 0.15 T<sub>bit</sub>. This lane-to-lane skew budget is in Inter-pair lane-to-lane 100 addition to skew between differenps T<sub>SKEW-INTER</sub> output skew tial input pairs Jitter budget for TMDS signals as Jitter added to TMDS 25 they pass through the level shifter.  $T_{JIT}$ ps signals 25ps = 0.056 at 2.25 Gbps

#### TMDS output oscillation elimination

The inputs already incorporate a squelch circuit. Therefore, nothing is needed from application standpoint to eliminate TMDS output oscillation when there is no TMDS input present. The IC will do this automatically.

| Symbol               | Parameter                                | Min | Тур | Max             | Units | Comments                                                                                                                           |

|----------------------|------------------------------------------|-----|-----|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IH-HPD</sub>  | Input High Level                         | 2.0 | 5.0 | 5.3             | V     | Low-speed input changes state on cable plug/<br>unplug                                                                             |

| V <sub>IL-HPD</sub>  | HPD_sink Input Low<br>Level              | 0   |     | 0.8             | V     |                                                                                                                                    |

| $I_{\text{IN-HPD}}$  | HPD_sink Input Leakage<br>Current        |     |     | 70              | μΑ    | Measured with HPD_sink at $V_{\text{IH-HPD}}$ max and $V_{\text{IL-HPD}}$ min                                                      |

| V <sub>OH-HPD</sub>  | HPD_source Output<br>High-Level          | 2.5 |     | V <sub>DD</sub> | V     | $V_{DD} = 3.3V \pm 10\%$<br>$I_{OH} = -4mA(MIN) / -8mA(MAX)$                                                                       |

| V <sub>OL-HPD</sub>  | HPD_source Output Low-<br>Level          | 0   |     | 0.4             | V     | $I_{OL} = 4mA(MIN) / 8mA(MAX)$                                                                                                     |

| $T_{ m HPD}$         | HPD_sink to HPD_source propagation delay |     |     | 200             | ns    | Time from HPD_sink changing state to HPD_source changing state. Includes HPD_source rise/fall time                                 |

| T <sub>RF-HPDB</sub> | HPD_source rise/ fall time               | 1   |     | 20              | ns    | Time required to transition from V <sub>OH-HPDB</sub> to V <sub>OL-HPDB</sub> or from V <sub>OL-HPDB</sub> to V <sub>OH-HPDB</sub> |

# $Dual\ Mode\ DisplayPort^{\text{\tiny TM}}\ to\ DVI/HDMI^{\text{\tiny TM}}\ Electrical\ bridge\ (Level\ Shifter)$

| Symbol            | Parameter                          | Min  | Тур | Max               | Units | Comments                                                                 |

|-------------------|------------------------------------|------|-----|-------------------|-------|--------------------------------------------------------------------------|

| $V_{\mathrm{IH}}$ | Input High Level                   | 2.0  |     | $V_{\mathrm{DD}}$ | V     | TMDS enable input changes state on cable plug/unplug                     |

| $V_{IL}$          | Input Low Level                    | 0    |     | 0.8               | V     |                                                                          |

| $I_{IN}$          | Input Leakage Current              |      |     | 10                | μΑ    | Measured with input at $V_{\text{IH-EN}}$ max and $V_{\text{IL-EN}}$ min |

| Table 5: Te       | ermination Resistor                |      |     | •                 | ·     |                                                                          |

| Symbol            | Parameter                          | Min  | Тур | Max               | Units | Comments                                                                 |

| R <sub>HPD</sub>  | HPD_sink input pull-down resistor. | 100K |     |                   | Ω     | Guarantees HPD_sink is LOW when no display is plugged in.                |

| Table 6: D          | Table 6: DDC I/O Voltage Levels (DDCBSEL = High) |      |      |      |       |                                                                                                                                         |  |  |  |

|---------------------|--------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol              | Parameter                                        | Min  | Тур  | Max  | Units | Comments                                                                                                                                |  |  |  |

| Vol_src             | Output voltage Low on<br>Source side             | 0.45 |      | 0.65 | V     | External pull-up to 3.3V from 1.5K $\Omega$ to 2K $\Omega$ ±5%, VOL_SRC - VIH_SRC > 50mV when pull up from 1.5K $\Omega$ to 2K $\Omega$ |  |  |  |

| Vol_snk             | Output voltage Low on Sink side                  |      |      | 0.20 | V     | External pull-up to 3.3V or 5V from 1.5K to 4.7K ±5%                                                                                    |  |  |  |

| $V_{\rm IL\_SRC}$   | Input voltage Low on Source side                 |      | 0.45 | 0.48 | V     | External pull-up to 3.3V from 1.5K $\Omega$ to 2K $\Omega$ ±5%                                                                          |  |  |  |

| V <sub>IL_SNK</sub> | Input voltage Low on Sink side                   |      | 1.5  |      | V     | External pull-up to 3.3V or 5V from 1.5K to 4.7K ±5%                                                                                    |  |  |  |

| Table 7: SQSEL  |                  |     |     |     |       |                          |  |  |  |

|-----------------|------------------|-----|-----|-----|-------|--------------------------|--|--|--|

| Symbol          | Parameter        | Min | Тур | Max | Units | Comments                 |  |  |  |

| V <sub>IH</sub> | Input High Level |     | 3.3 |     | V     | External pull-up to 3.3V |  |  |  |

| V <sub>IL</sub> | Input Low Level  |     | 0   |     | V     | Short to GND             |  |  |  |

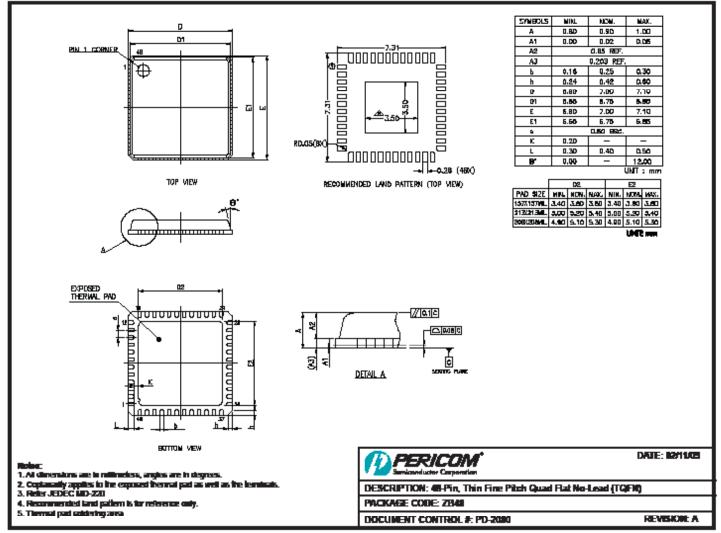

### Packaging Mechanical: 48-Pin TQFN (ZB)

#### 09-0091

#### Note:

- 1. For latest package info, please check: http://www.pericom.com/support/packaging/packaging-mechanicals-and-thermal-characteristics

- ${\bf 2. The\ exposed\ die\ paddle\ size\ is\ 3.6x3.6mm\ for\ PI3VDP411LSAZBE.}$

# **Ordering Information**

| Ordering Code   | Package Code | Package Type                 |

|-----------------|--------------|------------------------------|

| PI3VDP411LSAZBE | ZB           | Pb-free & Green, 48-pin TQFN |

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free and Green

- 3. Adding an X suffix = Tape/Reel

#### IMPORTANT NOTICE

- 1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- 9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-and-conditions/important-notice

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners.

© 2023 Diodes Incorporated. All Rights Reserved.

www.diodes.com