## AN1188

# **High-Side IntelliFET Application Note**

Mike Chen, DPNS, Diodes Incorporated

## **Table of Contents**

| 1. | INTRODUCTION                                                                        |

|----|-------------------------------------------------------------------------------------|

| 2. | INTELLIFET POWER STAGE                                                              |

|    | 2.1 Turn ON/OFF Characteristics with Resistive Load                                 |

|    | 2.2 Switching Behavior in PWM Operation                                             |

|    | 2.3 Power Dissipation Calculation4                                                  |

| 3. | LAMP LOADS, INDUCTIVE LOADS AND CAPACITIVE LOADS                                    |

|    | 3.1 Lamp Loads5                                                                     |

|    | 3.2 Inductive Loads                                                                 |

|    | 3.3 Capacitive Loads                                                                |

| 4. | PROTECTION FUNCTIONS                                                                |

|    | 4.1 Loss of Ground Protection7                                                      |

|    | 4.2 Loss of Battery Protection8                                                     |

|    | 4.3 Undervoltage Protection                                                         |

|    | 4.4 Overvoltage Protection9                                                         |

|    | 4.5 Load Dump Protection10                                                          |

|    | 4.6 Reverse Battery Polarity Protection10                                           |

|    | 4.7 Overload Protection11                                                           |

| 5. | DIAGNOSIS FUNCTIONS12                                                               |

|    | 5.1 SENSE Signal in Different Operating Modes12                                     |

|    | 5.2 Current Sense                                                                   |

|    | 5.3 IS pin Signal in the Nominal Current Range14                                    |

|    | 5.4 Open Load in ON Diagnostic14                                                    |

|    | 5.5 Open Load in OFF Diagnostic15                                                   |

|    | 5.6 Open Load Diagnostic Timing16                                                   |

| 6. | THE INPUT PINS16                                                                    |

|    | 6.1 Input Circuitry                                                                 |

| 7. | OTHER FREQUENTLY ASKED QUESTIONS OF INTELLIFET 17                                   |

|    | 7.1 How to Connect the DEN Pin when It Is Not Controlled by a Dedicated GPIB Port17 |

|    | 7.2 What to Do with IS Pin When It Is not used?17                                   |

|    | 7.3 How to determine if a condition is "output is short-to-battery"?                |

|    | 7.4 How to Eliminate Misjudgment in Open Load Diagnosis?                            |

| 8. | APPLICATION INFORMATION                                                             |

|    | 8.1 Application Circuit Examples20                                                  |

|    | 8.2 What to consider for PCB layout when using an IntelliFET?21                     |

|    | 8.3 How to Design PCB Land Pattern Both Single & Dual Channel Devices Can Use22     |

|    | 8.4 IntelliFET Family23                                                             |

## 1. Introduction

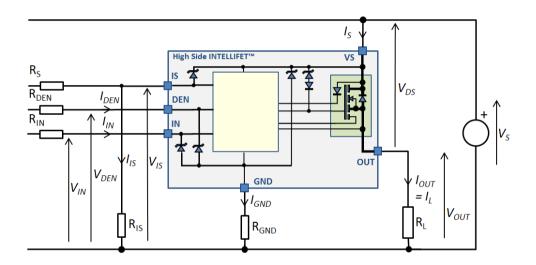

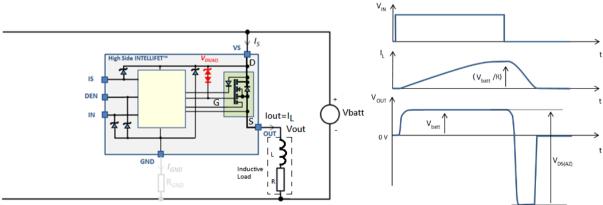

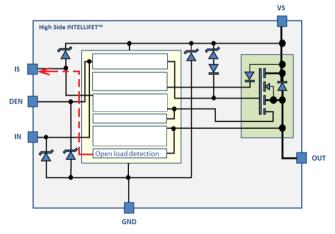

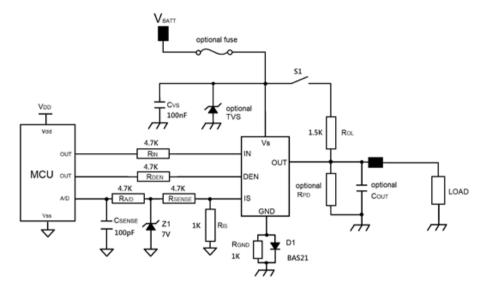

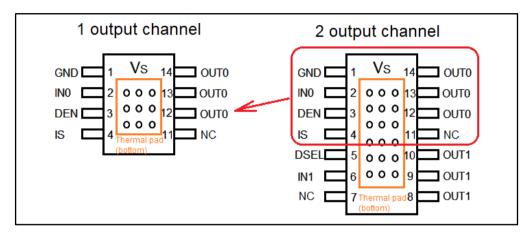

An IntelliFET<sup>®</sup> is a high-side power switch that comes in two different types: single channel type and dual channel type.

The single channel type of IntelliFET comprises a monolithic N-channel vertical power MOSFET and is in an SO-8 exposed heatsink package. The dual channel type has two N-channel MOSFETs which are in the SO-14EP package.

Both types of IntelliFETs have integrated temperature and current sensors with a charge-pumped gate drive power supply and have a low quiescent current in OFF state. Moreover, both parts incorporate plenty of protective and diagnostic functions.

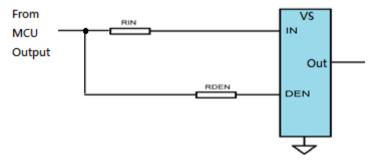

The single channel type of IntelliFET has an "IN" input pin which can be used to enable/disable the N-channel MOSFET. It also has a "DEN" input pin that can be used to enable/disable the IS pin. Both inputs can be enabled by active high 3.3V and 5V logic level.

The IS pin is connected to an internal diagnostic current source, which is proportional to load current and a defined diagnostic fault signal in case of overload operation, overtemperature, short-circuit or open load conditions.

The VS pin (the power pad), is the power source pin for the IntelliFET itself and is connected to the drain of the N-channel MOSFET. The OUT pins are connected to the source of the N-channel MOSFET and are the output pins of IntelliFET.

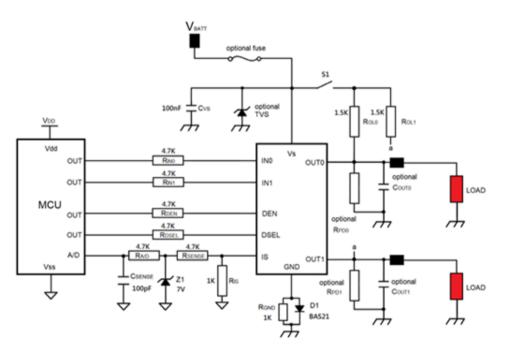

The dual channel type IntelliFET has a similar pin set to the single channel version. However, the dual channel type has two IN pins (\*IN0 and IN1) that can be used to enable/disable the individual channels. The two channels need to share one IS pin and one DEN pin. Nevertheless, the dual channel type IntelliFET has a unique "DSEL" pin which can be used to select which channel to diagnose.

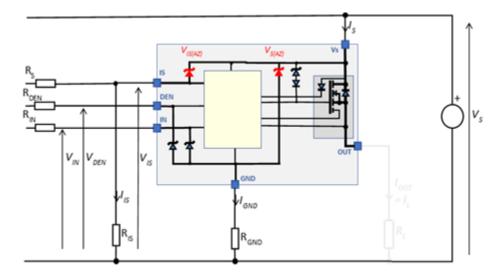

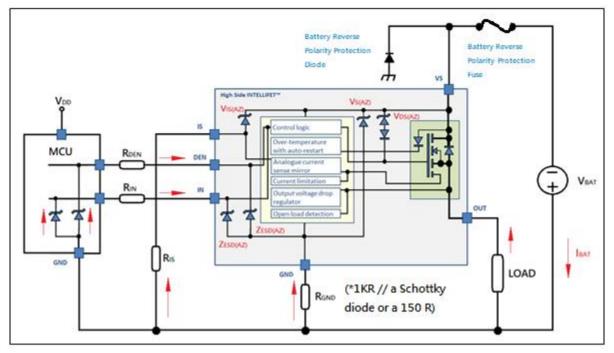

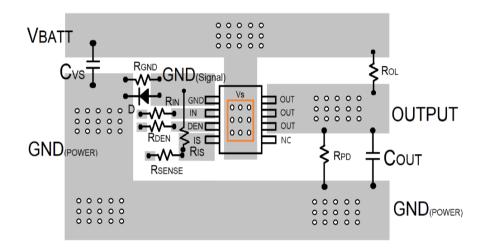

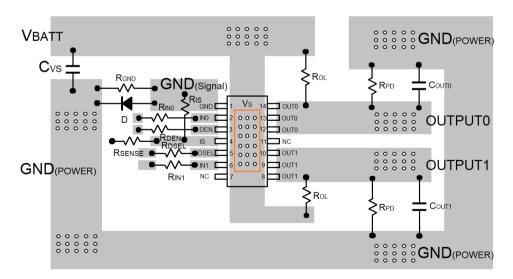

Figure 1. Application Example of IntelliFET

#### 2. IntelliFET Power Stage

## 2.1. Turn ON/OFF Characteristics with Resistive Load

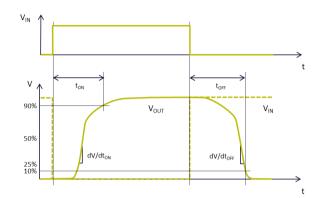

Figure 2 shows an example of the turn-on/turn-off characteristic waveform of an IntelliFET when driving a resistive load. All parameters of this graph are defined within IntelliFET datasheets. Compared with the turn-on/turn-off characteristic waveform of an ordinary MOSFET, it is obvious that the switching speed of IntelliFETs is quite slow. They are specially designed to reduce EMI and switching spike voltage.

Figure 2. Switching a Resistive Load

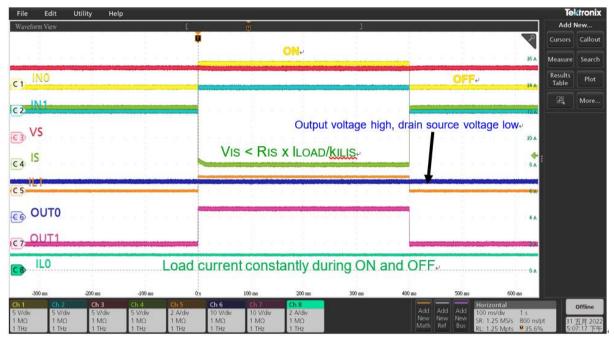

## 2.2 Switching Behavior in PWM Operation

Other than simply being used to turn on/off the load, IntelliFETs can also be used in PWM operation to control the output average voltage, for example, to control the temperature of a heater. However, there are some limitations of IntelliFETs that need to be considered when PWM operation is adopted. These are power loss, switching frequency availability, EMC emissions, and diagnostic limits. Power loss and switching time issues are described below.

As described in the previous section, the Vout of the IntelliFET does not increase very quickly when the IntelliFET is enabled, nor does the load current rise immediately. Please refer to Figure 2.

A similar situation occurs when the IntelliFET is disabled, but in this case, the Vout does not fall down quickly, and the current does not immediately fall down.

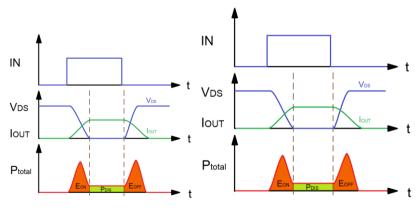

Again, these slow-switching speeds must be in automotive applications to ensure low EMI and voltage/current spikes. However, one of the costs of slow switching speed is higher switching losses. As shown in Figure 3, the current and voltage drop of the IntelliFET are both high during switching, which results in higher switching power loss =  $(V^* I)$  Integration.

Another tradeoff is the limited switching frequency: when the switching frequency is too high, the IntelliFET will be turned off before it is able to fully turn on. The maximum practical PWM frequency for IntelliFET is around 1K Hz in most cases (\*power consumption needs to be further evaluated).

Figure 3. IntelliFET PWM Control and Switching Losses Waveform

## 2.3 Power Dissipation Calculation

The steady-state power dissipated in the switch can be calculated by Equation (1):

$P_{SS} = I_{OUT}^{2} * R_{DS(ON)}$ (1)

If IntelliFET is turned on/off in a very low frequency, P<sub>SS</sub> is the total dissipation of IntelliFET. However, if it is PWM operation, switching energy loss should also be considered.

The switching energy losses:  $P_{SW} = (E_{ON} + E_{OFF}) * F_{SW}$  (2)

Note that both the EON & EOFF can be gotten by integrate the voltage \* current waveforms in switching.

The total power dissipation is:  $P_{TOT} = (P_{SW} + P_{SS})$  (3)

This is the overall loss for one channel. If the device has more than one channel, all the P<sub>TOT</sub> of each channel need to be summed up for junction temperature calculation.

To calculate the T<sub>J</sub> temperature of the IC, the ambient temperature T<sub>A</sub> is used, plus the power consumption multiplied by  $R_{\theta JA}$ . The formula is as shown below:

$T_{J} = T_{A} + (P_{TOT} * R_{\theta JA})$ (4)

#### 3. Lamp Loads, Inductive Loads and Capacitive Loads

InteliFETs can drive many kinds of loads. Among them, there are three types of loads that are more difficult to drive and therefore require design details. These loads are: Lamp loads, Inductive loads and capacitive loads.

#### 3.1 Lamp Loads

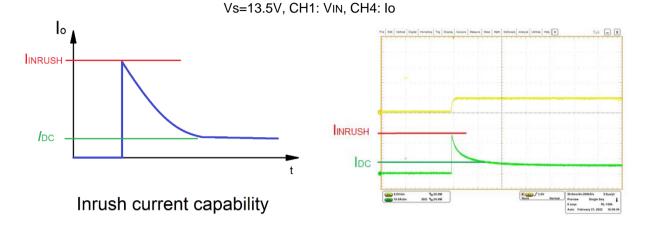

Figure 4. Bulb Inrush Current Capability

The impedance of a halogen bulb before lighting is quite low, which makes the bulb have a high inrush current (the peak may be several Amps to tens of Amps) at the beginning of lighting. But, as the filament ignites, the resistance of the bulb increases rapidly, and the current drops. This high peak current is the first consideration for lamp applications.

How to select an IntelliFET to drive a halogen bulb:

The first step is to know the peak current of the halogen bulb. This current can be measured at the highest battery voltage condition. Note that the colder the bulb, the higher the peak current. So, in evaluating the peak current, the ambient temperature for the bulb should be the lowest actual working temperature, and it should stop the test for enough time to cool down the bulb before next lighting.

The second step is to select the IntelliFET that meets the peak current demand according to the load current limit specification of the IntelliFET. Theoretically, it is best to choose an IntelliFET with a load current limit higher than the peak current, because this has the best reliability and there will be no flicker when the bulb is turned on.

#### **3.2 Inductive Loads**

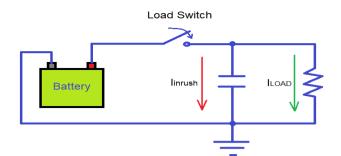

Figure 5. Switching an Inductive Load

Loads like chocks, relays, solenoids and motors have high inductance. Figure 5 shows us that if an IntelliFET turns off an inductor load, the load current is reduced. This reduction causes a negative rate of change current. **Note: (di/dt) value is negative.** According to Inductor Law, Vo = L(di/dt). Therefore, when (di/dt) is negative, the Vo will switch to negative in this situation and excessive negative voltage could cause the power FET to break down. To protect the power FET of IntelliFET against such breakdown, an internal clamp circuit between drain and source is implemented. The clamped voltage is named  $V_{DS(AZ)}$ .

This clamping action will turn the lethal breakdown energy of the inductance into a more acceptable conduction energy, E<sub>AZ</sub>, to the MOSFET.

$$E_{AZ} = \sim \left(\frac{V_{DS(AZ)}}{V_{DS(AZ)} - V_{batt}}\right) * L * \left(\frac{V_{batt}}{R}\right)^2$$

However, if  $E_{AZ}$  is too high, it will still damage the IntelliFET. A solution to this problem is to connect a freewheeling diode in parallel with the inductive load and add input resistors to the input pins and the GND Pin of this IntelliFET (\*Please refer to Figure 8).

When the IntelliFET is turned off, the instantaneous negative voltage of the OUT pin will be clamped by the diode, to a very low voltage,  $-V_f$  (the forward voltage of the freewheeling diode) and protect the MOSFET from avalanche breakdown. The input resistors of the input pins can also help to reduce the current's flow into the IC in this situation and protect these pins.

The  $V_f$ , forward voltage, of a diode is very low (often below one volt). Such a low reset voltage may cause a long reset time for the inductive load. If the long reset time is not acceptable, the diode can be replaced with a bidirectional TVS. This will change the reset voltage of the inductive load from  $V_f$  to the Clamping voltage of the TVS, thus speeding up the reset of the inductor.

When selecting the freewheeling diode or TVS, the **reverse breakdown voltage** of the diode (TVS) needs to be over the maximum battery voltage.

If a TVS is used, the TVS clamping voltage needs to < (the IntelliFET's minimum  $V_{DS(AZ)} - V_{Batt(max)}$ ). For example, if minimum  $V_{DS(AZ)}$  is ~41V and  $V_{Batt(max)}$  is 16V, the TVS clamping voltage needs to < 25V.

Note that the TVS clamping voltage is highly temperature dependent. In the example above, the TVS's clamping voltage needs to be <25V in any temperature condition. Please refer the datasheet of the TVS for the temperature coefficient of the clamping voltage.

For V<sub>batt(max)</sub>, please refer to <u>Load dump protection</u> for more consideration.

The **peak current rating** of the diode or the TVS needs to be higher than the peak inductor (load) current. The **power rating** needs enough to absorb the inductance energy. Moreover, if the load will be turned on/off many times in a short period of time; for example, with the solenoids of an ABS system, the diode or the TVS needs to be able to dissipate the accumulated energy, not just the energy of one switching cycle.

## 3.3 Capacitive Loads

In automotive applications, in order to reduce the input ripple voltage, many electronic modules adopt bulk input capacitors. These capacitor(s) can range from hundreds of microfarads to several tens of millifarads or even higher. When a load switch turns on to charge these bulky capacitors, it will experience a very high peak current, Inrush:

$$Iinrush = C \times \frac{dV}{dT}$$

(3)

Though the mechanism of the capacitive load is completely different from that of a lamp load, both have high inrush current. The method to select an adequate IntelliFET is also similar: First, measure the inrush current of the load. Second, chose an IntelliFET that has an adequate load current limit.

One difference is that many electronic modules cannot accept a "flickering" input voltage. Therefore, it is better for the load current limit of the IntelliFET to be "higher than" (not "close to") the current peak.

Figure 6. Capacitive Load Charging Diagram

## 4. Protection Functions

## 4.1 Loss of Ground Protection

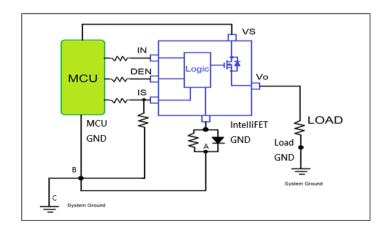

To explain what a "loss of ground" fault is, assume first, that there is a system which has an IntelliFET, an MCU that controls the IntelliFET, a load that is driven by the IntelliFET, and a metal chassis of an automobile, which is often referred to as the "system ground" of the system. There are several possible "loss of ground" conditions for this type of system.

The first condition is that the load ground is disconnected from the system GND. If the load is pure resistive or capacitive, this kind of "loss of the ground" is very safe: No device will burn, and the load is always in "off condition". If the load is inductive, but has a freewheeling diode (TVS), it will be safe too. No matter what type of load it is, the IntelliFET can diagnose this fault as an "open load" fault.

The second condition, is that the GND pin of the IntelliFET is disconnected from the system ground. If all the connections between the MCU and the IntelliFET have protective resistors, then both the MCU and the IntelliFET are safe. The IntelliFET will take this situation as a normal condition that both the VIN pin and the VDEN pin are "low" and turn off the internal MOS. Then, the load will also be turned off.

The third situation is that the connection between the MCU and the system "ground" is disconnected. This situation is more involved than the previous ones. If all connections between the MCU and the IntelliFET have protective resistors, the IntelliFET "itself" will be safe (not damaged). However, in this case, since the ground of the MCU becomes floating, the output voltage of the MCU will also float (unstable). If the MCU's output voltage exceeds the IntelliFET's VIN turn-on voltage, the IntelliFET will turn on the load and cause problems, such as a car horn that keeps honking, or a headlight that stays on and drains the battery.

In the above description, a serious "loss of the ground" failure mainly happens when the MCU and IntelliFET do not share the same ground. For this reason, it is recommended that the ground of an IntelliFET system be connected according to what is shown in Figure 7; Connect the IntelliFET GND pin to the MCU GND first. Then, connect the MCU GND to the system GND (the metal chassis). In this situation, no matter the IntelliFET ground wiring (\* A-B in figure-7), or the MCU ground wiring (\* B-C in figure-7) is disconnected, the output of the IntelliFET will always turn off, and none of the MCU, IntelliFET, or the load will fail.

Figure 7. Recommended Ground Connection for Better Loss of Ground Protection

| AN1188 – Rev 1   |

|------------------|

| Application Note |

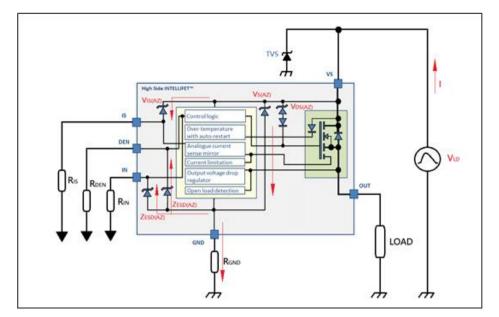

## 4.2 Loss of Battery Protection

A "loss of battery" fault will cut off the battery supply to the IntelliFET instantly and cause a very high (di/dt) situation.

This is a very dangerous situation if the load has high inductance (Please refer to the Inductive loads section). Additionally, when a "loss of battery" happens, the VS pin of the IntelliFET is not connected to anything, and the internal clamping circuit of the IntelliFET cannot function anyway.

Fortunately, an OUT pin freewheeling diode (or TVS) can still work for this kind of fault. Please also refer the <u>Inductive loads</u> section for the information about how to use a freewheeling diode (or TVS) for protection.

On the other hand, if the load is purely resistive or purely capacitive, even if the battery connection is cut off suddenly, no negative spike will occur. It is not necessary to add parallel diodes or TVSs for protection in this situation, unless the wiring inductance is very high.

Figure 8. Loss of Battery When Used Inductive Load

#### 4.3 Undervoltage Protection

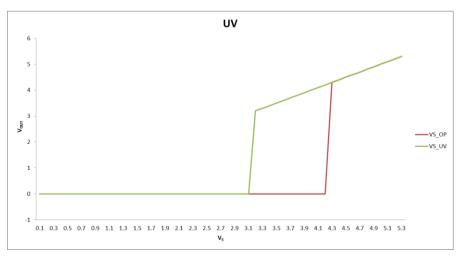

The device will not turn on if the Vs supply voltage is below the minimum operating voltage  $V_{S(OP)}$  where protection functions may not be operational. If the device is already on, then the supply voltage must drop to below the undervoltage threshold  $V_{S(UV)}$  to turn the output off. Figure 9 shows the undervoltage mechanism.

#### Figure 9. Undervoltage Behavior

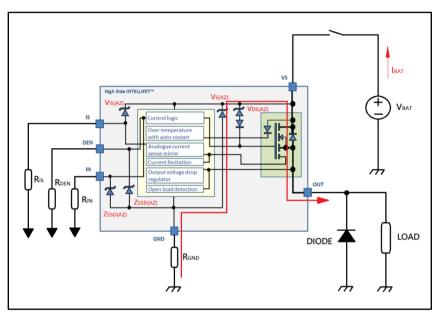

## 4.4 Overvoltage Protection

Figure 10. Overvoltage Clamping Circuit

The Vs pin has an internal active protection clamp, operating much like a low noise high voltage zener device. This internal clamp can protect the VS pin from overvoltage for high Vvs transients. During a Vvs transient overvoltage event, the voltage is clamped and the excess voltage, Vvs-V<sub>S(AZ)</sub>, is applied across the ground resistor R<sub>GND</sub> raising the potential on the GND pin. Additional high value resistors may be needed to prevent high V<sub>IN</sub> and V<sub>DEN</sub> being applied directly to the external driving circuits or MCU.

The IS pin also has an active protection clamp and during Vvs transient overvoltage the voltage is clamped and excess voltage, Vvs-V<sub>IS(AZ)</sub>, is applied across the sense resistor R<sub>IS</sub>. An additional high ohmic series resistor R<sub>S</sub> may be needed in the application to prevent high V<sub>IS</sub> being applied directly to the application monitoring circuit or MCU.

Figure 11. Typical Vvs-VIs Clamp Characteristic

Additionally, during  $V_{VS}$  overvoltage transient the voltage  $Vvs-V_{OUT}$  is clamped to  $V_{DS(AZ)}$  and the excess voltage,  $Vvs-V_{DS(AZ)}$ , is applied across the load  $R_L$ . Please refer the "Inductive loads" section for more detail.

Figure 12. Load Dump Protection

## 4.5 Load Dump Protection

In automotive applications, a load dump condition occurs when the alternator charges the battery with high current, but the battery is accidentally disconnected.

Load dumps can cause extreme overvoltage conditions: peak voltages can be as high as 120V and decay time up can be up to 400mS. To protect the electronic components on the car from this overvoltage condition, very large TVS devices are often installed near the car's alternator. However, more comprehensive protection can be provided if an additional TVS diode is added to the power input of each module, such as the VS Pin of IntelliFET.

The input TVS mentioned above can be an industry standard component such as the SMCJ28C/Q packaged in a 1.5kW (10/1000µs) rated SMC package. It can also be a more advanced, smaller, higher power TVS, such as the D28V0H1U2P5Q from Diodes Incorporated (Diodes). The D28V0H1U2P5Q can handle 20% more power than SMCJ28CA/Q does, while occupying only 40% of the PCB area. Please refer to <u>https://www.diodes.com/assets/App-Note-Files/TVS-in-Automotive-Applications.pdf</u> for more detail.

If Load Dump from an alternator occurs, it may keep the Vs Pin voltage at the clamping voltage of the above "Vs pin protecting TVS". This voltage is often much higher than the normal  $V_{Batt(max)}$ . This situation needs to be considered when deciding the clamping voltage rating, Vaz, of the freewheeling TVS that will be used.

## 4.6 Reverse Battery Polarity Protection

To prevent the IntelliFET from being damaged in reverse battery polarity conditions, one guideline is to place a resistor/diode network on the ground pin of the IntelliFET, as shown in Figure 13. Such a network can be as simple as a single  $150\Omega$  resistor (1206 size). A better solution is to use a Schottky diode in parallel with a 1 k $\Omega$  resistor. The anode of the Schottky is connected to the GND pin of the IntelliFET. The cathode is connected to the ground.

A Schottky in parallel with a 1K ohm resistor network is not expensive. It consumes almost no power during normal operation. This is due to the fact that during normal operation, the Schottky diode is forward biased to ground and bypasses the 1KR resistor. On the other hand, when it is in a reverse polarity condition, the 1KR resistor can limit the GND pin current to a lower (safer) level than what a 150R can do.

Besides the GND pin, the conditions of other pins of IntelliFET need also be considered and limited the abnormal currents with external resistors of adequate value. Please refer to the <u>ZXMS8 Series</u> of IntelliFET datasheets for the current limit of each pin.

Figure 13. Reverse Battery Polarity Protection

Figure 13 shows how to protect an IntelliFET from being damaged in reverse battery polarity condition. However, in a reverse polarity condition, the load current will flow through the body diode of the N-MOS channel of the IntelliFET to the battery. An IntelliFET can't turn off or limit this reverse current.

Extra protection(s) may be needed for load if reverse battery polarity could happen. For example, adding "input fuse and input reverse polarity diode (TVS)" to the load: If "reverse polarity condition" happens, high current will flow through the high-current diode (TVS) and blow out the fuse.

## 4.7 Overload Protection

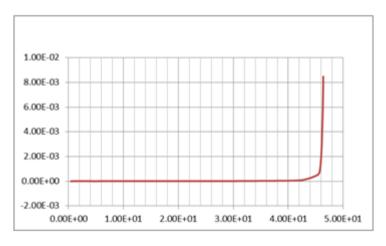

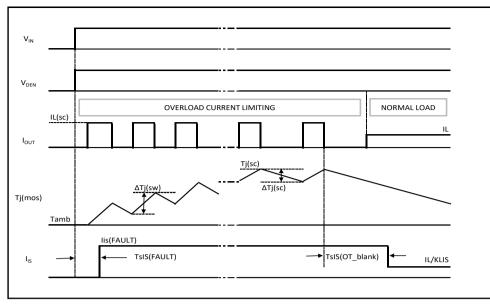

During overload, the output current is limited to a value depending on the V<sub>DS</sub> voltage and the load impedance. This high current results in high dissipation in the output power stage. Sustained operation in this mode will raise the junction temperature of the output MOS until dynamic or absolute overtemperature protection cycling begins. Figure 14 describes the overload protection.

IntelliFET has a dynamic ( $\Delta T_{J(SW)}$ ) and an absolute ( $T_{J(SC)}$ ) temperature sensor for overload detecting. If the "dynamic temperature rise" of the power stage versus the cooler control area exceeds  $\Delta T_{J(SW)}$ , the device will be turned off until the rise falls to a reset level. However, each such cycle will cause the absolute temperature to increase a little.

If the "absolute temperature" reaches  $T_{J(SC)}$  then the device will be turned off until the absolute temperature falls by  $\Delta T_{J(SC)}$ . The device will continue to cycle to  $T_{J(SC)}$  provided that the fault condition remains.

The IS pin will output a continuous current, I<sub>IS(FAULT)</sub> during: the load current limitation, dynamic overtemperature cycling, and absolute overtemperature cycling.

Figure 14. Overload Protection Timing Diagram

#### 5. Diagnosis Functions

In normal operation, the IS pin outputs a small analog sense current proportional to the main OUT current flowing in the power MOSFET. In the case where the current sense function is disabled by the DEN pin, the IS pin becomes high impedance.

During overload / current limit operation / overtemperature / high temperature gradient or open load in the OFF state, the IS pin outputs a defined current I<sub>IS(FAULT)</sub>. This special I<sub>IS</sub> is greater than the normal sense currents for normal loads.

During ON-state operation with open load, normal OFF-state, or OFF-state with inductive load ring-off current still flowing, the IS current is approximately zero.

For diagnosis purposes, IntelliFET provides a combination of digital and analog signals at the IS pin. In case the diagnostic is disabled via DEN, the IS pin becomes high impedance. In case DEN is activated, the IS of the channel is enabled, and will output different currents because of the IC working conditions. As for which channel of the dual-channel IntelliFET is to be diagnosed, it can be selected through the status of the DSEL pin. Please refer to Table 1 and Table 2 for the meaning of each IS pin current.

## 5.1. SENSE Signal in Different Operating Modes

| VDEN |   | IS output             |

|------|---|-----------------------|

| L    | Х | Z                     |

| H    | L | Channel 0 diagnostics |

| H    | H | Channel 1 diagnostics |

#### Table 1. Diagnostic Truth Table

| Operating Condition        | VINx | VDEN | Voutx      | IS output current, I <sub>IS</sub> |

|----------------------------|------|------|------------|------------------------------------|

| Normal operation           | L    | H    | Z          | Z                                  |

|                            | H    | H    | H          | = IL / KILIS                       |

| Current limiting           | Н    | Н    | Н          | I <sub>IS(FAULT)</sub>             |

| Short circuit OUT to GND   | L    | H    | L          | Z                                  |

|                            | H    | H    | L          | IIS(FAULT)                         |

| Over temperature           | L    | H    | Z          | Z                                  |

|                            | H    | H    | Z          | IIS(FAULT)                         |

| Short circuit OUT to $V_S$ | L    | H    | H          | IIS(FAULT)                         |

|                            | H    | H    | H          | < IL / KILIS (Note 1)              |

| Open load                  | L    | H    | < Vol(off) | Z                                  |

|                            | L    | H    | > Vol(off) | I <sub>IS(FAULT)</sub> (Note 2)    |

|                            | H    | H    | H          | < IIS(OL)                          |

| Inverse load current       | L    | H    | H          | IIS(FAULT)                         |

|                            | H    | H    | H          | IIS(OL)                            |

| All                        | Х    | L    | Х          | Z                                  |

#### Table 2. Operational Truth Table (Note 3)

#### Notes:

- 1. A low resistance short between OUT and VS will reduce the output current (IL), and therefore reduce the analog sense current (IIS).

- 2. With external pull-up resistor

- 3. H = high level; L = low level; Z = high impedance, voltage depends on external circuit; X = doesn't apply.

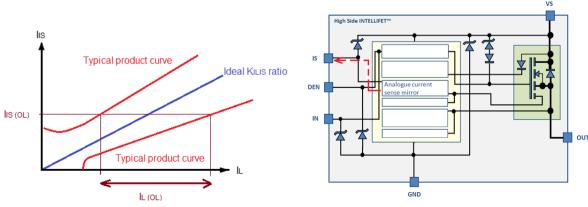

#### 5.2. Current Sense

In high-side power SW applications, the system designer often needs to know the amplitude of the load current. There are two methods that can be used for this purpose; using Hall sensors or shunt resistors to measure the current. However, the cost of the former is very high, and the latter must solve the problem of DC level shifting and extra power loss. Neither of the two is ideal.

To solve this problem, the IntelliFET IS pin provides a current sense information (IIS), which is a current proportional to the load current (IL):

$$I_{IS} = \frac{1}{K_{ilis}} \times I_L$$

The above IIS signals are useful under normal conditions. However, in exceptional cases, a "Fault" status flag would be more helpful to the system designer. IntelliFETs can meet this requirement by sourcing a "fault" status flag (IiS) current well above the maximum sense current value. This makes it easy to distinguish fault flags from normal detected currents.

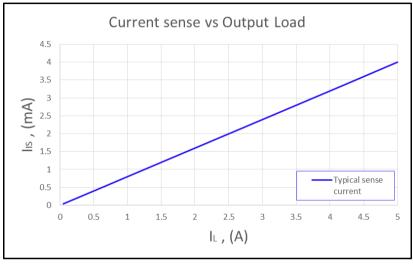

#### 5.3. IS pin Signal in the Nominal Current Range

Figure 15 is an example of the relationship between  $I_{IS}$  and  $I_L$  of IntelliFET under ideal conditions. The  $k_{ILIS}$  factor value in Figure 15 is ~1200.

When the  $I_{IS}$  signal is transferred into a more useful voltage format, a current sense resistor  $R_{IS}$  (\*Please refer the "Diagnostic Timing" section of the data sheet EC table for the typical  $R_{IS}$  value that can be used) is needed. This resistor ( $R_{IS}$ ) can convert the  $I_{IS}$  signal into voltage as  $V_{IS}$  (=  $I_{IS}$  \*  $R_{IS}$ ). Then, the MCU can get the load current information and fault status with an A/D converter (ADC). For the best measurement results, the ( $R_{IS}$ ) should be placed closely to the ADC pin of the MCU.

Figure 15. Current Sense for Nominal Load

#### 5.4 Open Load in IntelliFET ON-state Diagnostic

An MCU can be used to check if the load is open, by checking whether the current of the IntelliFET IS pin is lower than normal. The  $I_{IS(OL)}$  current of IntelliFET specification is recommended for use as the threshold for open load condition. If the IS pin current is below or equal to  $I_{IS(OL)}$  when DEN is selected (\*DEN pin is high), then MCU can take it as the sign that the load is open.

Ideally, the load current should be high when the load is normally connected. When open load occurs, the load current should drop to **zero**. The currents of the IS pin in these two conditions are very different, and are easily distinguishable. However, in practical cases, the current of some loads may be not very high, and when the load is open, the system may have some leakage current. In these two situations, the difference in the IS pin current can be so small that it is difficult to distinguish.

Moreover, the current sense ratio ( $K_{ILIS}$ ) of the IntelliFET chip is different from chip to chip. Figure 16 and table 3 provide more detail on this  $K_{ILIS}$  deviation. This deviation could make the open load judgment of the MCU incorrect, especially because the IS pin current difference is so small.

Figure 16. Open Load in ON state

|                                 | ZXMS  | ZXMS  | ZXMS  | ZXMS  | ZXMS  | ZXMS  |  |

|---------------------------------|-------|-------|-------|-------|-------|-------|--|

|                                 | 81045 | 81090 | 81200 | 82090 | 82120 | 82180 |  |

| k <sub>ı⊔ıs</sub> ratio typical | 1200  | 1460  | 300   | 1480  | 560   | 560   |  |

| I <sub>IS(OL)</sub> (μΑ)        | 8     | 8     | 33    | 8     | 22    | 22    |  |

| IL(OL) min (mA)                 | 5     | 5     | 5     | 5     | 5     | 5     |  |

| IL(OL) max (mA)                 | 30    | 30    | 15    | 30    | 30    | 30    |  |

#### Table 3. IntelliFET Open Load Definition

To eliminate the possible mistakes in open load judgment, it is necessary to set <u>the minimum load current</u> at a different amplitude than the <u>leakage current</u>. Please refer to the section <u>How to eliminate misjudgement in open load diagnosis</u> in this file for more detail.

## 5.5 Open Load in OFF Diagnostic

When in OFF Mode, the IntelliFET cuts off the current to the Out pin. At this time, if the load is connected to the Out pin, the voltage of the Out pin should be close to 0V. On the other hand, if the voltage of the Out pin is close to the VS pin, then the load should be open.

In actual application conditions, (in addition to the load current), the output pin may also have some leakage current to GND. Even if the load is open, this leakage current will pull the voltage of the OUT pin low, making it impossible for the IntelliFET to detect the open load. For this reason, it is recommended to add an external output pull-up resistor to eliminate leakage current effects.

As for how to select the resistance value of this pull-up resistor and how to avoid battery leakage caused by this resistor, please also refer to <u>How to eliminate misjudgement in open load diagnosis</u> section of this file for more detail.

Figure 17. Open Load in OFF state

## 5.6 Open Load Diagnostic Timing

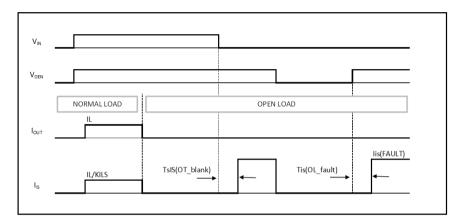

Figure 18, the open load timing diagram, shows the timing sequence for the detection under ON and OFF conditions.

In the "power stage" section of this application note, when Vin dropped, the Out voltage would drop, but the slew rate would be limited. This means that after Vin dropped, there will a short period of time when the Vo will still be "high". In order to blank this transient condition from causing a fault in "open load detecting", IntelliFET has an internal blank time tsIS(OL\_BLANK).

In some conditions, for example, when the input capacitance of a module is too high, tsIS(OL\_BLANK) may not be long enough. In these conditions, it is suggested to pull the DEN pin low at the same time when Vin drops. Then, wait for a while to let the OUT voltage drop to low. Next, turn the DEN voltage to enable an open loop diagnostic. The fault caused by insufficient tsIS(OL\_BLANK) blanking time can be prevented with this method.

Figure 18. Signal Open Load Timing Diagram

#### 6. The Input Pins

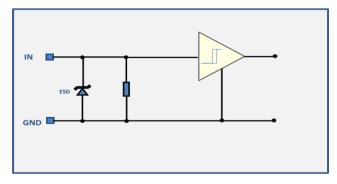

#### 6.1 Input Circuitry

Figure 19 shows the electrical equivalent input circuitry of the average IntelliFET. The input circuitry is compatible with 3.3V and 5V microcontrollers. The input signal is either OFF or ON but cannot be in a linear or undefined state. A Schmidt trigger is used to avoid any undefined state if the voltage on the input pin is slowly increasing or decreasing. The input circuitry is compatible with PWM applications. In case the pin is not needed, it must be left opened, or be connected to IntelliFET GND pin (not MCU ground).

Figure 19. Input Pin Circuitry

## 7. Other Frequently Asked Questions of IntelliFET

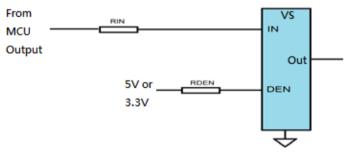

#### 7.1. How to Connect the DEN Pin when It Is not Controlled by a Dedicated GPIB Port

When a system designer wants to know the load current of an IntelliFET, they can use an A/D converter (ADC) to monitor the IS pin of the IntelliFET. However, when a system uses many IntelliFETs, monitoring each IntelliFET by an independent ADC may be impossible. In this case, all of the IS pins can be connected to the sensing resistor of one ADC. Then, the GPIO channels can be used to enable the DEN Pin of the IntelliFET that needs to be monitored (\*keep the DEN pin voltage of the unselected IntelliFET low). What the ADC reads at this time is the status of the selected IntelliFET. This method can greatly save the ADC numbers needed to monitor the IS pins.

However, in some cases, it is the GPIO numbers that need to be reduced. For example, when the MCU has enough ADCs to monitor each IntelliFET, the DEN pins of these IntelliFETs can be connected to a fixed 3.3V or 5V voltage source (= IntelliFET always selected). This can save one GPIO channel per each IntelliFET.

If there is no fixed 3.3V or 5V voltage source available, the DEN pin can be shorted to the Vin pin of the same IntelliFET. The disadvantage of this method is that three diagnostic functions are only available when VIN=High: (A) Short Circuit OUT to Vs, (B) Open Load, and (C) Inverse load current. However, this method also has its advantage: If only one IntelliFET's Vin is High at one time, one ADC can be used to monitor several IntelliFETs.

If the system uses many IntelliFETs, it is recommended to use a logic gate IC, like 2\_to\_4 decoder (or 3\_to\_8, 4\_to\_16... etc.) to increase the available GPIB channel number.

Figure 20. Connecting DEN Pin to a Fixed V Source

Figure 21. Connecting DEN Pin to The IN pin

#### 7.2. What to do with IS pin when it is not used?

For better PCB mounting, solder this pin to its soldering pad. However, there is no need to connect the soldering pad to any other point of the circuit.

7.3 How to determine if a condition is "output is short-to-battery".

Figure 22. Electrical Signals in Normal Load and Short-to-Battery Condition

When the output is ON and the load is shorted to the battery (=VS) via a low impedance loop, this condition can be easily determined: The  $I_{IS}$  in this short-circuit condition will be much lower than the normal  $I_{IS}$ , because this short circuit loop will share most of the load current. The current flow through the IntelliFET will then decrease.

If the resistance of the above short circuit loop is higher, the  $I_{IS}$  in this situation could be very close to the normal  $I_{IS}$ , and this short circuit condition is difficult to distinguish from a normal condition. When the output is off, this "higher resistance short circuit" fault is very easily detected. It will be similar to an "open load in off-state", whereas an external pull-up resistor is connected to the OUT pin. Please refer the "open load in off-state" related sections of this application note for more detail.

However, if the impedance of the short circuit loop is too high (up to several  $k\Omega$  or higher), it is possible that the IntelliFET will not be able to distinguish this kind of short circuit from a potential battery-to-load leakage.

## 7.4. How to Eliminate Misjudgement in Open-Load Diagnosis

## 7.4.1. Open Load in the "ON" Condition

Below is an example of how to eliminate misjudgment in open-load diagnosis in the "On" condition:

Table 4 shows the open-loop detecting threshold of ZXMS81045. If the minimum load current is less than IL(OL) max =30mA, it can be seen that the lis(OL) of some IntelliFET Ics will be less than  $8\mu$ A (\*the recommended threshold for open load detecting). The MCU will mistakenly think that an open loop has occurred.

On the other hand, if the system leakage current is higher than IL(OL) min = 5mA, (even if open load occurs), the lis(OL) of some IntelliFET Ics will still be greater than  $8\mu$ A. Under this condition, the MCU will mistakenly think that the open loop did not happen.

If the ZXMS81045 in the above example were to be replaced with the ZXMS81200, then the IL(OL) max can be reduced to 15mA. Reducing system leakage can make the open loop current <5 mA. Doing these two things can avoid misjudgement by the MCU.

| Symbol              | Parameter                             | Conditions                                                               | MIN | ТҮР | MAX | Unit |  |  |  |

|---------------------|---------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

| Open Load Detection |                                       |                                                                          |     |     |     |      |  |  |  |

| V <sub>DS(OL)</sub> | Open load OFF state detection voltage | V <sub>IN</sub> = 0 V, V <sub>DEN</sub> = 4.5 V                          | 3.5 | -   | 4.5 | V    |  |  |  |

| IL(OL)              | Open load ON state detection current  | V <sub>IN</sub> = V <sub>DEN</sub> = 4.5 V<br>I <sub>IS(OL)</sub> = 8 μA | 5   | -   | 30  | mA   |  |  |  |

Table 4.

Parameter: Open Load Detection Threshold in ON State

#### 7.4.2. Open load in the "OFF" Condition

In some applications, it may be necessary to know whether the load is open even when the IntelliFET is OFF, for example, to know if the solenoids of an ABS braking system is open. In this situation, the following methods can be used for detection:

First, connect the OUT pin of the IntelliFET to the battery supply with a high value resistor. When the IntelliFET is OFF and the load is not open, the load impedance should pull the voltage on the OUT pin close to GND. On the other hand, when the load is open, the pull-up resistor will pull the voltage of the OUT pin close to the battery voltage. When IN pin voltage is low, and DEN pin voltage is High, as long as  $(V_{VS} - V_{OUT}) < V_{DS(OL)}$ , IntelliFET will send IS pin current =  $I_{L(OL)}$ . When the MCU detects this current, it knows that an open circuit has occurred.

The value of the external pull-up resistor needs to be determined carefully, according to the application: The current needs to be small enough (usually a few milliamps), to reduce power loss and not activate the load during detection. On the other hand, the current also needs to be large enough that any existing normal level of leakage current will not be considered a load presence condition. Note, that when the battery voltage changes, the load current and leakage current also change. When selecting the value of the external pull-up resistors, both the highest and lowest battery states must be considered.

The problem with using the pull-up resistor is that it will cause battery leakage when the IntelliFET is OFF. If the user finds it necessary to eliminate this leakage, a switch can be added between the pull-up resistor and the battery. It is only necessary to turn on this switch when performing open circuit detection; this will solve the leakage problem. This switch can be a relay, a PNP transistor, a PMOS, or even a photocoupler.

Examples of the open load detection at "OFF" for a single output and for multiple device or outputs are shown in Figure 23 and 24. A transistor switch S1 in between the  $R_{OL}$  and the battery can be used to turn off the detecting current when not in detecting period.

## 8. Application Information

## 8.1. Application Circuit Examples

Figure 23. Single Channel Application Circuit

Figure 24. Dual Channel Application Circuit

Notes:

- 4. The above application circuits, Figure 23 and 24, are for reference only. They must be modified to meet the different requirements of real applications.

- 5. A 1µF capacitor can be placed in parallel with the RGNS of Figure 23 and 24 to eliminate the noise on RGND.

## 8.2. What to consider for PCB layout when using an IntelliFET

Please refer to the example PCB layout below to better understand the guidelines here:

- RIN, RDEN, R<sub>DSEL</sub> should be placed as closed to the digital input pins (IN, DEN, DSEL) as possible, to decrease

parasitic capacitance effect.

- Place RGND and D as close as possible to the device.

- <u>Place RSENSE and RIS to be close to the MCU ADC pin (Not IS pin)</u>. This is because the function of RSENSE and RIS is to transfer the IS pin current into a voltage format for the ADC pin. Placing them close to the ADC pins reduces ground noise and induced noise.

- Place Vs capacitor and Vout capacitor as close as possible to the device.

- Put more thermal via around exposed pad, to reduce both the loop impedance and the thermal impedance.

- For thermal pad layout, see the below figure for the best system performance.

- Place at least 2 via for the GND connection of each Vs capacitor and Vout capacitor. The via should be placed as close to the capacitors as possible.

Figure 25. Layout suggestions for single channel IntelliFET

Figure 26. Layout Suggestions for Dual Channel IntelliFET

#### 8.3 How to Design a PCB Land Pattern that both Single Channel and Dual Channel Devices can use.

In some applications, different but similar modules must share one bare PCB. Some of these modules may need a single channel IntelliFET, whereas others may need the dual channel version. This requirement can be satisfied by adopting the land pattern of the dual channel IntelliFET in PCB design, because the upper half land pattern of a dual-channel IntelliFET is identical to that of a single-channel version (please refer Figure 27). For IntelliFET products, NC pins are not used. To enhance soldering strength, all NC pins must be soldered to PCB GND.

Figure 27. Pin-out of Single Channel and Dual channel IntelliFET

## 8.4. IntelliFET Family

|                                                                 |                           | ZXMS     | ZXMS      | ZXMS      | ZXMS      | ZXMS       | ZXMS      |       |

|-----------------------------------------------------------------|---------------------------|----------|-----------|-----------|-----------|------------|-----------|-------|

| Parameter                                                       | Symbol                    | 81045    | 81090     | 81200     | 82090     | 82120      | 82180     | Unit  |

| KILIS ratio (typ)                                               | KILIS                     | 1200     | 1480      | 300       | 1500      | 550        | 550       | -     |

| Power Dissipation<br>(Max)                                      | Ртот                      | 1.6      | 1.6       | 1.6       | 1.9       | 1.8        | 1.6       | W     |

| Energy dissipation<br>(single pulse) (Max)                      | E <sub>AS</sub>           | 40       | 40        | 40        | 42        | 15         | 30        | mJ    |

| Junction to ambient<br>Thermal impedance<br>(Typ) (Notes 1 & 2) | R <sub>thJA</sub>         | 42       | 42        | 42        | 47        | 47         | 46        | °C/W  |

| On-state resistance<br>(150°C)                                  | P                         | 90 (Max) | 200 (Max) | 400 (Max) | 180 (Max) | 240 (Max)  | 360 (Max) | mΩ    |

| On-state resistance<br>(25°C)                                   | R <sub>DS(ON)</sub>       | 34 (Тур) | 90 (Typ)  | 200 (Тур) | 75 (Typ)  | 100 (Тур)  | 150 (Тур) | 11122 |

| Nominal load current                                            | I <sub>L(NOM)</sub> _1 ch | 4        | 3         | 1.5       | 3.5       | 2.5        | 2         | •     |

| (Тур)                                                           | I <sub>L(NOM)</sub> _2 ch | -        | -         | -         | 2.5       | 2          | 1.5       | A     |

| Inverse output current<br>(Typ)                                 | -I <sub>L(INV)</sub>      | 3        | 2.5       | 1         | 2.5       | 2          | 1.5       | A     |

| Switch ON energy<br>(Typ)                                       | Eon                       | 0.8      | 1.1       | 0.19      | 0.7       | 0.4        | 0.4       | mJ    |

| Switch OFF energy<br>(Typ)                                      | Eoff                      | 0.7      | 0.8       | 0.16      | 0.8       | 0.3        | 0.4       | mJ    |

|                                                                 |                           | 25 (Min) | 15 (Min)  | 6 (Min)   | 17 (Min)  | 10 (Min)   | 8 (Min)   |       |

| Load current limit<br>(*Vs=5V)                                  | I <sub>L5(SC)</sub>       | 32 (Typ) | 23 (Typ)  | 9 (Typ)   | 25 (Typ)  | 13.5 (Typ) | 11 (Typ)  | А     |

|                                                                 |                           | 40 (Max) | 30 (Max)  | 12 (Max)  | 34 (Max)  | 17 (Max)   | 15 (Max)  |       |

| Load current limit<br>(*Vs=28V), (typ)                          | I <sub>L28(SC)</sub>      | 16       | 15        | -         | 18        | 7          | 5         | A     |

| Load current during<br>over-temperature<br>cycling, (typ)       | I <sub>L(RMS)</sub>       | 4        | 3         | 2         | 3         | 2          | 2         | A     |

| Open load I <sub>IS</sub><br>threshold in ON state<br>(typ)     | lis(ol)                   | 8        | 8         | 33        | 8         | 22         | 22        | μA    |

| I <sub>L</sub> for K <sub>ILIS</sub> 0                          | ILO                       | 0.05     | 0.05      | 0.01      | 0.05      | 0.05       | 0.05      | А     |

| I∟ for Kı∟ıs1                                                   | IL1                       | 0.5      | 0.5       | 0.05      | 0.5       | 0.25       | 0.25      | А     |

| I∟ for Kı∟ıs2                                                   | IL2                       | 1        | 1         | 0.2       | 1         | 0.5        | 0.5       | А     |

| I∟ for Kı∟ıs3                                                   | I <sub>L3</sub>           | 2        | 2         | 0.5       | 2         | 1          | 1         | А     |

| IL for KILIS4                                                   | I <sub>L4</sub>           | 4        | 4         | 1         | 4         | 2          | 2         | A     |

#### Table 5. Summarizes the Differences between Different IntelliFET

Notes:

Not subject to production test, guaranteed by design

Device mounted on vertical PCB, 2" x 2" x 1.6 mm, FR4 with 2oz copper for all connections.

#### IMPORTANT NOTICE

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications; (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5 Diodes' Diodes' products are provided subject to Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated. All Rights Reserved.

#### www.diodes.com