## AN1159

# **DGD2106M Application Information**

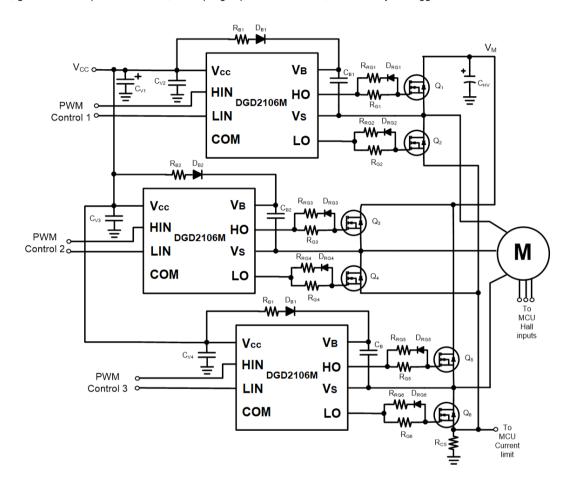

The DGD2106M, high-side/low-side gate driver is used to optimally drive the gate of MOSFETs or IGBTs. Below (Figure 1) is an example application using DGD2106M with MOSFETs to make three half-bridge circuits used to drive a three phase motor. Typical motor applications are AC Induction motors, PMSMs, and BLDC motors. DGD2106M can also be used in power supplies. In this document, the important parameters needed to design in the DGD2106M are discussed. Main sections are bootstrap resistor, diode, and capacitor selection, gate driver component selection, decoupling capacitor discussion, and PCB layout suggestions.

Figure 1. Three Phase Motor Driver application example of DGD2106M

## **Bootstrap Component Selection**

#### **Bootstrap Resistor**

Considering Figure 1, when the low-side MOSFET (Q2, Q4, or Q6) turns on, Vs pulls to GND and the bootstrap capacitor ( $C_{B1}$ ,  $C_{B2}$ , or  $C_{B3}$ ) is charged. When the high-side MOSFET (Q1, Q3, or Q5) is turned on,  $V_S$  swings above Vcc and the charge on the bootstrap capacitor ( $C_B$ ) provides current to drive the IC high-side gate driver. The first charge of  $C_B$  from Vcc through the bootstrap resistor ( $R_{BS1}$ ,  $R_{BS2}$ , or  $R_{BS3}$ ) and bootstrap diode ( $R_{BS1}$ ,  $R_{BS2}$ , or  $R_{BS3}$ ) occurs when power is first applied and the low-side turns on the first time. At this time the charge current is the largest as typically  $R_{BS2}$  is not discharged fully at each cycle during normal operation.

A bootstrap resistor ( $R_{BS}$ ) is included in the bootstrap circuit to limit the inrush current that charges  $C_B$  when Vs pulls below Vcc; this inrush current is largest with the first charge. Limiting inrush current is desirable to limit noise spike on Vs and COM, potentially causing shoot-through. The amplitude and length of time of the inrush current is determined mostly by the component value of  $R_{BS}$  and  $C_{BS}$  as well as Vcc level. The aim in resistor selection for the application is to slow down the inrush current but have minimal effect on the RC time constant of charging  $C_{BS}$ .

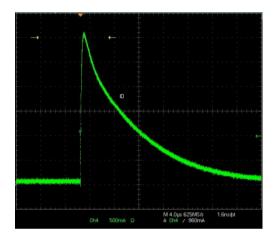

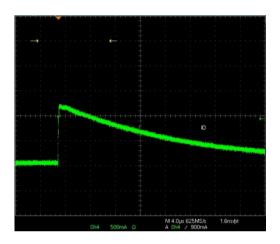

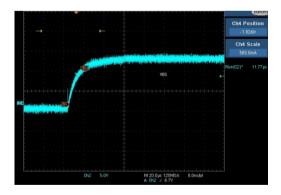

Typically, values for  $R_{BS}$  are  $3\Omega$  to  $10\Omega$ , enough to dampen the inrush current but have little effect on the  $V_{BS}$  turn on. Figures 2-5 illustrate the effect of different  $R_{BS}$  values.

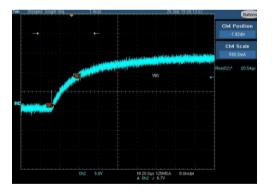

Figure 2. Bootstrap Peak inrush current  $\approx$ 3A with RBS=3 $\Omega$ , CBS=2.2 $\mu$ F

Figure 3. Bootstrap Peak inrush current ≈1.2A with RBS=10Ω, CBS=2.2μF

Figure 4. VBS Rise Time (11.8 $\mu$ s) with RBS=3 $\Omega$ , CBS=2.2 $\mu$ F

Figure 5. VBS Rise Time (20.5 $\mu$ s) with RBS=10 $\Omega$ , CBS=2.2 $\mu$ F

#### **Bootstrap Diode**

The chosen bootstrap diode ( $D_{BS}$ ) should be rated higher than the maximum rail voltage since the diode must be able to block the full rail voltage and any spikes seen at the  $V_S$  node. The diode's current rating is simply the product of total charge (QT) required by the HVIC (High Voltage Integrated Circuit) and the switching frequency. An ultrafast recovery diode is recommended to minimize any delay of charging the  $C_{BS}$  cap. A 1A ultrafast recovery diode is typical for DGD2106M applications.

#### **Bootstrap Capacitor**

The initial step in determining the value of the bootstrap capacitor is to determine the minimum voltage drop ( $\Delta V_{BS}$ ) that can be guaranteed when the high-side device is turned on. In other words, the minimum gate-source voltage ( $V_{GS\_min}$ ) must be greater than the UVLO of the high-side circuit, specifically  $V_{BSUV}$  level. Therefore, if  $V_{GS\_min}$  is the minimum gate-source voltage such that:

$V_{GS min} > V_{BSUV}$

Then:

$\Delta V_{BS} = V_{CC} - V_f - V_{GS min} - V_X$

#### Where:

- Vcc is the supply voltage to the DGD2106M

- V<sub>f</sub> is the voltage drop across the bootstrap diode (D<sub>BS</sub>)

- V<sub>X</sub> is the voltage drop across the MOSFET

$V_X$  is calculated as the current seen across low-side MOSFET multiplied by its  $R_{DS\_ON}$  and is simply  $V_{CE\_ON}$  at the specific output current if an IGBT were used instead.

In addition to the voltage drops across these components, other factors that cause  $V_{BS}$  to drop are leakages, charge required to turn on the power devices, and duration of the high-side on time. The total charge (QT) required by the gate driver then equals:

$$Q_T = Q_G + Q_{LS} + [I_{LK\_N}] * T_{H\_ON}$$

Where:

Q<sub>G</sub> = gate charge of power device

Q<sub>LS</sub> = level shift charge required per cycle

$T_{H\_ON}$  = high-side on time

$I_{LK_N}$  = sum of all leakages that include:

- I<sub>GSS</sub>/I<sub>GES</sub>: Gate-source leakage of the power device

- I<sub>LK\_DB</sub>: Bootstrap diode leakage

- I<sub>LK\_IC</sub>: Offset supply leakage of HVIC

- I<sub>Q\_BS</sub>: Quiescent current for high-side supply

- I<sub>LK\_CB</sub>: Bootstrap capacitor leakage

Bootstrap capacitor leakage ( $I_{LK\_CBS}$ ) only applies to electrolytic types. Therefore, it is best not to use an electrolytic capacitor. Thus, bootstrap capacitor leakages will not be included in the calculations.

Q<sub>LS</sub> is not listed in the datasheet; depending on the process technology, it could range anywhere from 3-20nC for 500V to 1200V process respectively. Assuming a value of 10nC for the 600V process should be sufficient with added margin.

From the basic equation, then the minimum bootstrap capacitor is calculated as:

$C_{B \text{ min}} \ge Q_T / \Delta V_{BS}$

Example using MOSFET, DMNH6021SK3Q

HVIC=DGD2106M

Vcc = 12V

$Q_G = 20nC$

$I_{GSS} = 100nA$

$T_{H\_ON} = 10 \mu s$

$R_{DSON} = 25m\Omega \text{ max}, 125^{\circ}C$

lout = 5A

$I_{Q_BS} = 130 \mu A$

$I_{LK\_IC} = 50\mu A$

$Q_{LS} = 10nC$

$V_F = 1.0V$

I<sub>LK\_DB</sub> = 100μA

$V_{GSmin} = 10.0V$

From equations:

$\Delta V_{BS} = 12V - 1.0V - 10V - (0.125V) = 0.875V$

$Q_T = Q_G + Q_{LS} + (I_{LK_N} * T_{H_ON})$  where  $I_{LK_N} * T_{H_ON} = 2.8nC$

= 20nC + 10nC + 2.8nC

= 32.8nC

Thus  $C_{BS}$  min = 32.8nC/0.875V = 37nF.

The bootstrap capacitor calculated in the above example is the minimal value required to supply the needed charge. It is recommended that a margin of 2-3 times the calculated value be used. Utilizing values lower than this could result in over charging of the bootstrap capacitor especially during –VS transients.

Typically for motor driver applications  $C_{BS} = 1\mu F$  to  $10\mu F$  are used. It is recommended to use low ESR ceramic capacitors as close to the  $V_B$  and  $V_S$  pin as possible (see PCB layout suggestions section).

### **Gate Resistor Component Selection**

The most crucial time in the gate drive is the turn on and turn off of the MOSFET, and performing this function quickly, but with minimal noise and ringing is key. Too fast a rise/fall time can cause unnecessary ringing and poor EMI, and too slow a rise/fall time will increase switching losses in the MOSFET.

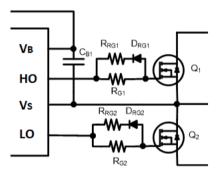

Figure 6. Gate Drive High-Side and Low-Side Components for DGD2106M

Considering the gate driver components for DGD2106M in Figure 6, with the careful selection of  $R_{\text{Gn}}$  and  $R_{\text{RGn}}$ , it is possible to selectively control the rise time and fall time of the gate drive to the MOSFET Qn. For turn on, all current will go from the IC through  $R_{\text{G1}}$  and charge the MOSFET gate capacitance, hence increasing or decreasing  $R_{\text{Gn}}$  will increase or decrease rise time in the application. With the addition of  $D_{\text{RGn}}$ , the fall time can be separately controlled as the turn off current flows from the MOSFET gate capacitor, through  $R_{\text{RGn}}$  and  $D_{\text{RGn}}$  to the driver in the IC to VS for high-side and COM for low-side. So, increasing or decreasing  $R_{\text{RGn}}$  will increase or decrease the fall time. Sometimes finer control is not needed and only  $R_{\text{G1}}$  and  $R_{\text{G2}}$  is used.

Increasing turn on and turn off has the effect of limiting ringing and noise due to parasitic inductances, hence with a noisy environment, it may be necessary to increase the gate resistors. Gate component selection is a compromise of faster rise time with more ringing, and a poorer EMI but better efficiency, and a slower rise time with better EMI, better noise performance but poorer efficiency. The exact value depends on the parameters of the application and system requirements. Generally, for motors the switching speed is slower, and the application has more inherent noise, higher values are recommended, for example  $R_G = 20\Omega - 100\Omega$ .

To have equal switching times for high-side and low-side, it is recommended that the gate driver components for high-side and low-side are mirrored. For example  $R_{RG1} = R_{RG2}$ ,  $D_{RG1} = D_{RG2}$  and  $R_{G1} = R_{G2}$ .

## **Decoupling Capacitor Selection**

For optimal operation, Vcc decoupling is crucial for all gate driver ICs. With poor decoupling, larger Vcc transients will occur at the IC when switching, and for greater and longer Vcc drops the IC can go into UVLO.

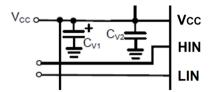

Figure 7. Suggested Vcc decoupling

As shown in Figure 7, two decoupling capacitors are recommended  $C_{V1}$  and  $C_{V2}$ .  $C_{V1}$  can be a larger electrolytic, for example 47µF (50V), and is used to dampen low frequency drains on supply:  $C_{V1}$  does not need to be right next to the IC, but  $C_{V2}$  is used to decouple faster edge changes to Vcc, and should be a low ESR ceramic capacitor placed close to the Vcc pin. This component provides stability when Vcc is quickly pulled down with load from the IC. Typical values for  $C_{V2}$  are  $0.1\mu\text{F}$  to  $1\mu\text{F}$ .

For applications with multiple gate driver ICs (for example BLDC motor drive with 3 x gate drivers as shown in Figure 1), one larger electrolytic ( $C_{V1}$ ) can be used and the three low ESR ceramic caps ( $C_{V2}$ ,  $C_{V3}$ ,  $C_{V4}$ ) should be used close to the Vcc pin (see Layout section also).

## **Input Resistors**

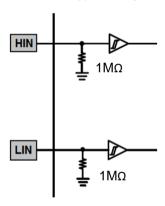

The DGD2106M PWM inputs, HIN and LIN, are very high impedance inputs with a pull-down resistor on both inputs to COM (see Figure. 8). The pull-down resistor on HIN and LIN has a value of approximately  $1M\Omega$ .

Figure 8. Input Logic for DGD2106M

## **Matching Gate Driver with MOSFET or IGBT**

#### IC drive current and MOSFET/IGBT gate charge

Gate Driver ICs are defined by their output drive current, its ability to source current to the gate of the MOSFET/IGBT at turn on and to sink current from the gate of the MOSFET/IGBT at turn off. For the DGD2106M, the drive current is  $I_{O+}$ =290mA typical and  $I_{O-}$ =600mA typical.

For a given MOSFET/IGBT, with the known drive current of the DGD2106M, you can calculate how long it will take to turn on/off the MOSFET/IGBT with the equation:

t = Qq/

$\mbox{Qg} = \mbox{total charge of the MOSFET/IGBT}$  as provided by the datasheet I = sink/source capability of the gate driver IC t = calculated rise/fall time with the given charge and drive current

For example with the Diodes' DGTD65T15H2TF, 650V IGBT, Qg = 61nC; and with the DGD2106M  $I_{O+}$ =290mA and  $I_{O-}$ =600mA, the tr = 210ns and tf = 102ns. These are estimates as the total charge given in the datasheet may not be the same conditions in the application. Also, an addition of a gate resistor will increase the tr and tf.

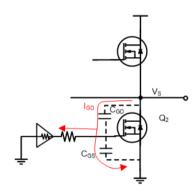

#### Unexpected shoot-through with dV<sub>DS</sub>/d<sub>t</sub>

Unwanted MOSFET turn-on, caused by  $C_{\text{GD}} \times dV_{\text{DS}}/d_t$  (see Figure 9) is often the cause of unexplained shoot through in the half-bridge circuit. Depending on the ratio of  $C_{\text{GS}}/C_{\text{GD}}$ , when the  $dV_{\text{DS}}/d_t$  across low-side MOSFET (Q2) occurs (i.e when high-side MOSFET turns on), there can be a voltage applied to the gate of the Q2 MOSFET, turning on Q2 and causing shoot through. In effect a gate bouncing occurs causing a ringing on the VS line and the power ground.

Figure 9. Unexpected shoot through with  $dV_{DS}/d_t$

Considering Figure 9,

$I_{GD} = C_{GD} \times dV_{DS}/d_t$

$I_{\text{GD}}$  will flow towards the resistive load (and small inductance due to parasitics) of the gate driver and the  $C_{\text{GS}}$  of the MOSFET. Hence this unwanted condition may be minimized by looking at the Ciss/Cres in the MOSFET datasheet (Ciss/Cres gives an indication of  $C_{\text{GS}}/C_{\text{GD}}$ ); having a Ciss/Cres as large as possible will minimize this phenomenon. Also an external capacitor can be added to the gate-source of the MOSFET (for example 1nF) which will increase  $C_{\text{GS}}/C_{\text{GD}}$ .

## **Minimum Pulse Requirement**

The DGD2106M has RC filters on the input lines to be more resilient in noisy environments. With a rising edge at the input to the gate driver, followed by the propagation delay of the IC, delay from gate resistor, and rise time of the MOSFET, the half-bridge will then turn on producing bus voltage at the output. This MOSFET turn on produces significant system noise. For optimal operation, it is suggested to provide a minimum pulse width at the input to the IC from the MCU to ensure the turn off occurs after this event. As a rule of thumb, this minimum pulse should be 2 x propagation delay for high-side/low-side gate drivers; hence for the DGD2106M, the minimum pulse recommended at the logic inputs is 440ns.

During typical operation, the DGD2106M will respond to an input greater than 50ns (approximate value from the RC input filter response). Hence for an input pulse greater than 50ns approximately the IC will follow the pulse as expected; and for an input pulse less than 50ns, there will be no response from the IC.

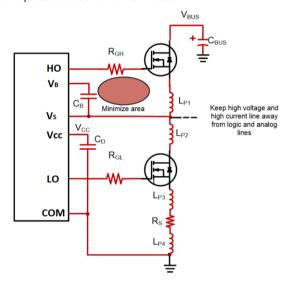

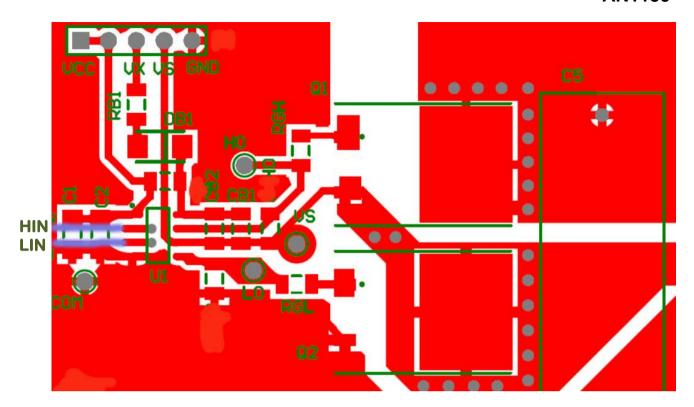

## **PCB** layout suggestions

Layout plays an important role in minimizing unwanted noise coupling, unpredicted glitches, and abnormal operation which can arise from a poor layout of the associated components. Figure 10 shows a schematic with parasitic inductances in the high-current path ( $L_{P1}$ ,  $L_{P2}$ ,  $L_{P3}$ ,  $L_{P4}$ ), which would be caused by inductance in the metal of the trace. Considering Figure 10, the length of the tracks in red should be minimized, and the bootstrap capacitor ( $C_B$ ) and the decoupling capacitor ( $C_D$ ) should be placed as close to the IC as possible in addition to using low ESR ceramic capacitors. And finally, the gate resistors ( $R_{GH}$  and  $R_{GL}$ ) and the sense resistor ( $R_S$ ) should be surface mount devices. These suggestions will reduce the parasitics due to the PCB traces.

Figure 10. Layout suggestions for DGD2106M in a half-bridge, lines in red should be as short as possible.

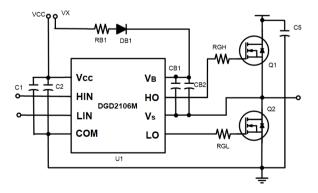

Figure 11. Schematic for layout example in Figure 12.

Fig 12. Layout of the schematic shown in Figure 11, DGD2106M in SOIC8.

All routing and components on top except for HIN and LIN from input

#### **IMPORTANT NOTICE**

- 1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (<a href="https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/">https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/</a>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2021 Diodes Incorporated

www.diodes.com