# GreenPacket<sup>™</sup> PCI Express® Packet Switch – Digital Video Surveillance System

Pericom Devices: PI7C9X20505GP and PI7C9X20508GP – 5-Port 5-Lane, and 5-Port 8-Lane PCI Express Packet Switch

#### **Overview**

A digital video surveillance system typically includes one or multiple cameras connected to a Video Surveillance Card. A Video Surveillance Card is a device that converts analog video streams to digital format. The hardware and software of the surveillance system then process the digital output from the Video Surveillance Card for display, storage, or other applications.

Many video surveillance systems are designed to integrate multiple cameras. Each camera supplies a separate analog feed to the Video Surveillance Card. The video decoder device converts the feed from analog form to digital format. Depending on the video decoder model, each decoder can decode 1 to 4 feeds simultaneously. If the number of the cameras required in a system exceeds the maximum that a video decoder can support, multiple video decoder devices are needed.

### **Pericom Solution**

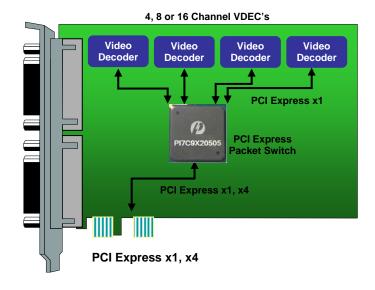

With more video decoder devices going from PCI interface to native PCIe®, the design of the video surveillance boards is evolving from PCIe Bridge to PCIe Packet Switch. In response to the trend, Pericom offers PCIe packet switches as a solution to integrate multiple PCIe video decoder devices in a single video surveillance card.

In a multiple video decoder configuration, a PCIe packet switch is used to fan out a single PCI Express port to connect to multiple video decoder devices. The block diagram shows a typical overview of a native PCIe Video Surveillance card. Pericom's Packet Switches can help expand the connectivity to accommodate the need for multiple video encoders.

## **Key Features & Specification**

- Supports "Cut-through" (Default) as well as "Store and Forward" mode for packet switching

- Peer-to-peer switching between any two downstream ports

- 150 ns typical latency for packet routed through Switch without blocking

- Strapped pins configurable with optional EEPROM

- Compliant with System Management (SM) Bus, Version 1.0

- Compliant with PCI Express Base Specification Revision 1.1

- Compliant with PCI Express CEM Specification Revision 1.1

- Compliant with PCI-to-PCI Bridge Architecture Specification Revision 1.2

- Compliant with Advanced Configuration Power Interface (ACPI) Specification

- Compliant with PCI Standard Hot-Plug Controller (SHPC) and Subsystem Specification Revision 1.0

- Reliability, Availability and Serviceability

Supports Data Poisoning and End-to-End CRC

Advanced Error Reporting and Logging

Hot Plug support

IEEE 1149.6 JTAG interface support

Advanced Power Saving

Empty downstream ports are set to idle state to minimize power consumption

Any downstream port enters L1 or ASPM L1, the clock to corresponding circuits is turned off

Link Power Management

Supports L0, L0s, L1, L2, L2/L3Ready and L3 link power states

Active state power management for L0s and L1 states

Beacon or Wake# support in L2 state

Device State Power Management

Supports D0, D3Hot and D3Cold device power states

3.3V Aux Power support in D3Cold power state

- Port Arbitration: Round Robin (RR), Weighted RR and Time-based Weighted RR

- Extended Virtual Channel capability

Two Virtual Channels (VC) and Eight Traffic Class (TC) support

Disabled VCs' buffer is assigned to enabled VCs for resource sharing

Independent TC/VC mapping for each port Provides VC arbitration selections: Strict Priority, Round Robin (RR) and Programmable Weighted RR

Supports Isochronous Traffic

Isochronous traffic class mapped to VC1 only Strict time based credit policing

- Supports up to 256-byte maximum payload size

- Programmable driver current and de-emphasis level at each individual port

- Industrial Temperature Range -40 to 85°C

AN225 09/02/08

### PI7C9X20505GP

- 5-lane PCI Express Switch with 5 PCI Express ports

- Non-blocking full-wired switching capability at 20 Gbps when all 5 ports are enabled

- Low Power Dissipation at 0.75W in L0 normal mode

- 256-pin PBGA 17mm x 17mm package, 1.0 mm Ball Pitch

#### PI7C9X20508GP

- 8-lane PCI Express Switch with 5 PCI Express ports

- Non-blocking full-wired switching capability at 32 Gbps when all 5 ports are enabled

- Low Power Dissipation at 1.0W in L0 normal mode

- 256-pin PBGA 17mm x 17mm package, 1.0 mm Ball Pitch

## **Product Status and Pricing**

- Samples Now

- Production Now

- OEM retail pricing in 10Ku quantities:

- o PI7C9X20505GP \$9.5

- o PI7C9X20508GP \$10.5

#### **Additional Information**

- Website

- Datasheets, Production Briefs, Application Notes

- http://www.pericom.com/products/packetswitch/index.php

### **Contact Information**

Please contact your local Pericom Sales Representative or franchised distributor. Contact list provided on the website:

http://www.pericom.com/partners/

## **Application Support**

http://www.pericom.com/contact/support.php

# **GreenPacket<sup>™</sup> PCI Express Switch Product Family**

| Part Number                 | PI7C9X20404GP      | PI7C9X20505GP      | PI7C9X20508GP               |

|-----------------------------|--------------------|--------------------|-----------------------------|

| Ports                       | 4                  | 5                  | 5                           |

| Lanes                       | 4                  | 5                  | 8                           |

| Configuration               | 1 x1 Up, 3 x1 Down | 1 x1 Up, 4 x1 Down | 1 x1 or x4, Up 4 x1<br>Down |

| Power<br>Typ. (W)           | 0.65               | 0.75               | 1.0                         |

| Advanced Power Saving       | Yes                | Yes                | Yes                         |

| Virtual Channel (VC)        | 2                  | 2                  | 2                           |

| Traffic Class (TC)          | 8                  | 8                  | 8                           |

| Latency<br>Typ. (ns)        | 150                | 150                | 150                         |

| Package                     | LFBGA 148          | PBGA 256           | PBGA 256                    |

| Package Size (mm)           | 12x12              | 17x17              | 17x17                       |

| Ball Pitch (mm)             | 0.8                | 1.0                | 1.0                         |

| Bandwidth Mgmt (QoS)        | Yes (API)          | Yes (API)          | Yes (API)                   |

| Isochronous Traffic Support | Yes (VC1)          | Yes (VC1)          | Yes (VC1)                   |

| Signal Integrity            | Programmable       | Programmable       | Programmable                |

| Payload Size                | 256B               | 256B               | 256B                        |

| SMBus                       | Yes                | Yes                | Yes                         |

| Co-Footprint                | N/A                | Yes                | Yes                         |

| GPIO                        | 8                  | 8                  | 8                           |

AN225 09/02/08