#74

## User Guide for PI7C8148 Reference Board

By: Jay Jung

#### Introduction

The Pericom PI7C8148 PCI bridge evaluation board demonstrates the bridge and allows testing of key features either before or during design / layout stages. The PI7C8148 PCI Bridge complies with PCI Local Bus Specification Revision 2.2, PCI-to PCI Bridge Architecture Specification Revision 1.1 and PCI Power Management Interface Specification Revision 1.1.

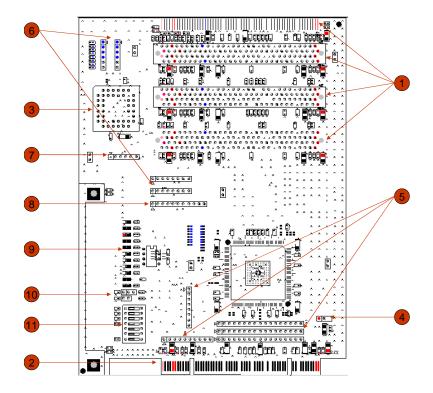

#### Quick start (photo of PI7C8148 reference board)

The numbers on the photo correspond to the text explanation on the right:

- 1) 3 standards and one straddle mount PCI connector.

- 2) Pin 1 on the golden PCI edge connector faces left when looking down on the component (bridge IC).

- 3) External arbiter socket

- 4) Secondary bus Vio select: 3.3V or 5V

- 5) Primary bus test points

- 6) Secondary bus test points

- 7) JTAG connector

- 8) GPIO & Hot Swap test points

- 9) Power, GPIO & Hot Swap Led indicator

- 10) Hot Swap eject switch

- 11) Switches to set internal arbiter disable/enable, bus mode settings and some misc. functions

This board comes **already configured** to support:

- a) Secondary PCI voltage (S\_VIO) is set to 3.3V.

- b) Internal arbiter is enable

- c) Hot Swap eject switch is pulled high.

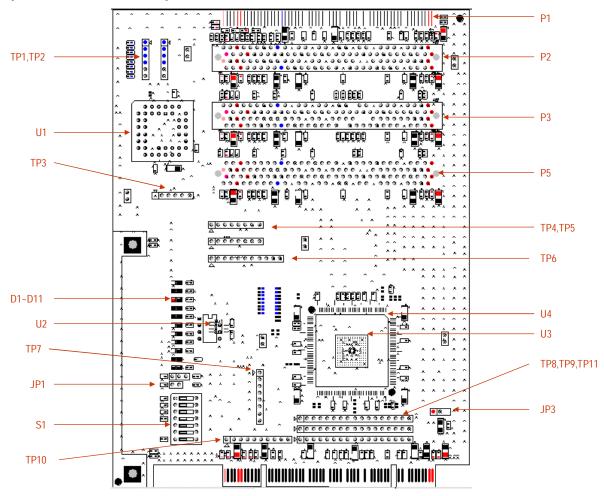

### **Components and Jumper Reference**

| U1<br>U2<br>U3<br>U4                           | Socket for optional external arbiter<br>Serial ROM for 8148 configuration<br>Pericom PI7C8148 Bridge<br>FPGA160 for testing usage |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| P1<br>P2<br>P3<br>P5                           | Secondary bus slot 3 Secondary bus slot 2 Secondary bus slot 1 Secondary bus slot 0                                               |

| TP1, TP2<br>TP4, TP5<br>TP3<br>TP6<br>TP7~TP11 | Secondary bus test points  JTAG connector GPIO & Hot Swap test points Primary bus test points                                     |

| D1~D11                                         | Power, GPIO & Hot Swap LED indicator                                                                                              |

| JP1<br>JP3                                     | Hot Swap eject switch<br>SVIO 3.3V or 5V select                                                                                   |

| <b>S</b> 1                                     | Switches to set internal arbiter disable/enable, bus mode settings and some misc. functions                                       |

#### TABLES:

- a) The right side of the board has a table of test points TP8, TP9 and TP11.

- b) The component U1, U4 and TP3 is for special testing usage. And there is no any side effect for this unconnected part.

Please contact Pericom if you have any requirement for this issue.

## Application Note

#74

#### Default Switch and Jumper Settings at a Glance

| <b>S</b> 1 | Signal       | Default | Description (ON: 'Low' or 'Connect', OFF: 'High' or 'Disconnect')              |  |  |  |  |

|------------|--------------|---------|--------------------------------------------------------------------------------|--|--|--|--|

| 1          | BPCCE        | OFF     | 'OFF' - when PI7C8148 is under the D2 or D3 hot power state, the secondary bus |  |  |  |  |

|            |              |         | will be placed at the B2 power state.                                          |  |  |  |  |

| 2          | S_CFN#       |         | For special testing usage                                                      |  |  |  |  |

| 3          | SCAN_TM#     | OFF     | 'OFF' – for normal operation, scan chain disable                               |  |  |  |  |

| 4          | CTRL_S_M66EN | OFF     | 'OFF' – Put the secondary bus clock is under the 66Mhz                         |  |  |  |  |

| 5          | S_M66EN      | OFF     | 'OFF' – Disconnect the S_M66EN with the CTRL_S_M66EN setting                   |  |  |  |  |

| 6          | EDGE_M66EN   | OFF     | 'OFF' – Disconnect the S_M66EN with the primary bus M66EN setting              |  |  |  |  |

| 7          | EDGE_PME#    | OFF     | 'OFF' – Disconnect the S_PME# with the primary bus <i>PME#</i> setting         |  |  |  |  |

JP1 Eject switch is pulled high.

JP3 SVIO configured to 3.3V

### Before Powering the Board

a) Seat the board into a PCI slot on the main system board.

Please look from the front of the motherboard, the small lip on our reference board points to the back of the motherboard, and the component side with the PI7C8148 bridge chip is on the left hand side.

b) Connect any PCI cards desired on the secondary PCI bus.

For all PCI connectors on our reference board, when looking down onto the PI7C8148 Bridge IC, pin 1 is on the left side of the board. This also applies to the top mounted "straddle" connector. Also each PCI connector has "A1", "B1", "A62", "B62" at the 4 corners of each slot, as a reminder where pin 1 is on each connector.

At this time, the Pericom PI7C8148 reference board is ready to use.

# Application Note

#74

## Primary Bus Test Points – TP8, TP9 and TP11:

For allowed a logic analyzer or oscilloscope to monitor signals on the path between the PI7C8140 and the primary bus. There are 3 rows of 17 pin connectors, labeled TP8, TP9 and TP10

|      | 1     | 2    | 3    | 4     | 5    | 6    | 7      | 8      | 9     |

|------|-------|------|------|-------|------|------|--------|--------|-------|

| TP8  | GNT#  | AD30 | AD27 | AD24  | AD22 | AD19 | AD16   | IRDY#  | STOP# |

| TP9  | REQ#  | AD29 | AD26 | CBE3# | AD21 | AD18 | CBE2#  | TRDY#  | LOCK# |

| TP11 | AD31  | AD28 | AD25 | AD23  | AD20 | AD17 | FRAME# | DEVSEL | PERR# |

|      |       |      |      |       |      |      |        |        |       |

|      | 10    | 11   | 12   | 13    | 14   | 15   | 16     | 17     |       |

| TP8  | SERR# | AD15 | AD12 | AD9   | AD7  | AD3  | AD1    | GND    |       |

| TP9  | PAR   | AD14 | AD11 | CBE0# | AD6  | AD5  | AD0    | GND    |       |

| TP11 | CBE1# | AD13 | AD10 | AD8   | AD4  | AD2  | IDSEL  | GND    |       |

#### **Test Points Description:**

For allowed convenient sampling of signals by logic analyzer or oscilloscope:

| TP1,  |                |               |                 |                  |                 |           |           |              |                 |

|-------|----------------|---------------|-----------------|------------------|-----------------|-----------|-----------|--------------|-----------------|

| TF 1, | 1              |               | 2               |                  | 3               | 4         |           | 5            | 6               |

| TP1   | TP1 SLOT_REQ2# |               | SLOT_GNT2#      |                  | SLOT_REQ3#      | SLOT_GNT3 | #         | GND          | GND             |

| TP2,  |                |               | _               | •                |                 | _         | •         |              |                 |

|       | 1              |               | 2               |                  | 3               | 4         |           | 5            | 6               |

| TP2   | TP2 SLOT_REQ0# |               | SLOT_GNT0#      |                  | SLOT_REQ1#      | SLOT_GNT1 | #         | GND          | GND             |

| TP3,  |                |               |                 |                  |                 |           |           |              |                 |

|       | 1              |               | 2               |                  | 3               | 4         |           | 5            | 6               |

| TP3   | VCC            |               | TCK             |                  | TDI             | TDO       |           | TMS          | GND             |

| TP4,  |                |               |                 |                  | _               |           |           |              |                 |

|       | 1              | 2             | ;               | 3                | 4               | 5         | 6         | 7            | 8               |

| TP4   | S_IDSEL3       | S_IDSEL2      | _IDSEL2 S_IDSE  |                  | S_IDSEL0        | P_CLKRUN# | S_CLKRUN# | gND          | GND             |

| TP5,  |                |               |                 |                  |                 |           |           |              |                 |

|       | 1              | 2             | 3               |                  | 4               | 5         | 6         | 7            | 8               |

| TP5   | S_RST#         | S_CLKOUT      | S_CL            | COUT2            | S_CLKOUT1       | S_CLKOUT0 | GND       | GND          | GND             |

| TP6,  |                |               |                 |                  |                 |           |           |              |                 |

|       | 1              |               | 2               |                  | 3               | 4         |           | 5            | 6               |

| TP6   | GPI            | O3            | GPIO2           |                  | GPI01           | GPI00     |           | EPCLK        | EEPD            |

|       |                |               | 8               |                  | 9               | 10        |           | 11           |                 |

| TP6   | 7<br>ENUM#     |               | EJECT           |                  | 9<br>L_STAT     | GND       |           | 11<br>GND    | -               |

| TP7,  | LIVO           | 14111         | LJLOT           | <u> </u>         | <u> </u>        | GND       |           | GIVE         | J               |

| ,<br> | 1              |               | 2               |                  | 3               | 4         |           | 5            | 6               |

| TP7   | BPCCE          |               | S_CFN#          |                  | SCAN_TM#        | SCAN_E    | N S       | 5_M66EN      | S_PME#          |

|       |                |               |                 |                  |                 |           |           |              |                 |

| 7     |                |               | 8               |                  |                 |           |           |              |                 |

| TP7   | GN             | ט ן           | GND             |                  |                 |           |           |              |                 |

| TP10, |                |               | 2               |                  | 2               | 1 4       |           |              | T ,             |

| TP10  | 1<br>EDCE 1    | NIT A #       | 2<br>EDGE_INTB# |                  | 3<br>EDGE_INTC# | EDGE_INT  | ID# ED    | 5<br>GE_PME# | 6<br>EDGE_M66EN |

| 1710  | EDGE_I         | EDGE_INTA# ED |                 | E_INTO# EDGE_INT |                 | EDGE_IIV  | ID# EL    | GL_PIVIE#    | LDGE_IVIOUEIN   |

|       | 7              |               | 8               |                  | 9               | 10        |           |              |                 |

| TP10  | TP10 P_RST#    |               | P_CLK           |                  | GND             | GND       |           |              |                 |

# Application Note

#74

### **Special Concerns**

Due to test purpose, the 8148 reference board leaves some part for specific experiment. And these unconnected parts can not impact the system any more. Please contact with the Pericom if you need any help for this issue.

Please reference the following unconnected part list:

- 1) C100

- 2) CT1~CT17

- 3) JP2

- 4) RNS1~RNS11

- 5) R76, R85

- 6) TP3

- 7) U1, U4