# 700 Series 20V BIPOLAR ARRAY DESIGN MANUAL

Last Revision Date: 2 December 2005

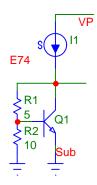

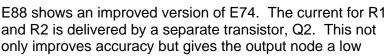

The 700 Series Design Manual has been originated and is maintained by Hans Camenzind, Array Design Inc. San Francisco. Feedback is welcome. Array Design offers design assistance for users or potential users of the 700 Series (generally free of charge), as well as full custom designs in bipolar, CMOS and BICMOS technology.

See also the book "Designing Analog Chips" at <a href="http://www.designinganalogchips.com/">http://www.designinganalogchips.com/</a>, a free download. This book can also be purchased in printed form.

Array Design Inc. 332 Virginia Ave. San Francisco CA 94110-5151 415-308-6090 camenzind@arraydesign.com Blank page.

## Semicustom Chips

When you begin the design of an electronic product, you have the choice of putting it together from standard (or discrete) parts available off a distributor's shelf or to employ Application Specific Integrated Circuits (ASICs). In this first chapter we will explore and dissect the various kinds of ASICs and compare them with discrete designs.

The oldest among ASICs is the full *custom* IC. Here all the layers are specifically designed for you. The supplier will, most likely, use an already proven process, but all the masks (up to perhaps 15) must be specifically designed and made and are used for only one product: yours.

The great advantage of a custom IC is its density. It has been designed to do *one* specific job. All components on the chip are there for a purpose and the designer need not expand the capability of the chip to include as many applications as possible, as is the case for a standard IC.

There are, however, four major disadvantages to custom ICs. First, the development time is the longest among all ASICs, mainly because all layers have to be designed from ground up and wafers have to be processed all the way through. Second, the development is the riskiest: one mistake in any of the layers and your circuits won't work. Third, the development cost is high, owing to the extended design time, the fabrication of many masks and the pilot processing of wafers. And fourth, using a special mask for each processing step makes fabrication of small quantities difficult and costly.

The next category in ASICs uses *standard cells*. In this approach the *design* is economized by dividing the circuit into repeatable cells. Once these standard cells are developed, a layout can be put together very rapidly and the chances of making a mistake are greatly reduced. This approach has also been dictated by the use of the computer: a full custom circuit, where each device is hand-designed, requires an inordinate amount of memory;

in standard cell ICs a cell must be described fully only once and can be repeated with simple coordinates.

However, one of the major disadvantages of full-custom ICs remains for the standard cell design. While the cells may be standardized, their placement and routing is not. Therefore, a full set of custom masks is still required and is reflected in high cost for anything but large manufacturing quantities.

Also, standard cells are well-suited only for digital ICs, where most designs can be based on gates. For linear designs it is much more difficult to create a cell which can be regarded as standard. Just about any design requires a different speed, power consumption, precision, operating voltage, input impedance, output drive, slew rate, offset voltage etc. In addition there are many functional blocks which are unique to a particular application.

The third category within ASICs are *semicustom ICs*. Here the gates (in digital ICs) or components (in linear ICs) are pre-designed, they are in fixed locations on the chip. All the designer needs to do is to interconnect them in his or her own way.

In the simplest form only one layer, the next to last one, needs to be customized. Thus the manufacturer needs only one mask, the metal mask, to produce a unique circuit on a standardized wafer.

The chief advantages of semicustom ICs are:

- 1. The development cycle is far shorter compared to custom or standard cell ICs. The wafers can be pre-processed and inventoried at the point were customization begins; the finishing of the wafer then requires only a small fraction of the total processing time.

- 2. The development cost is much lower compared to custom or standard cell ICs. Only one mask needs to be custom-designed.

- 3. **Semicustom is the lowest-risk approach**. The chances of making a mistake are reduced by the number of layers. The devices upon which the design is based are well characterized and can be used to breadboard or computer-simulate the design. Changes, if necessary, can be made easily and at minimum cost.

- 4. It is the only approach which makes it possible to design an integrated circuit without previous IC design experience. Having the devices pre-designed lets you concentrate on circuit design.

5. The semicustom approach works well for even small production quantities. It is a relatively easy task to draw a fully diffused, standard wafer from inventory and pattern it with a custom mask.

The main *disadvantage* of semicustom ICs is usually perceived to be their larger required area, because not all of the devices on the chip are used. Thus one is tempted to conclude that semicustom ICs only have a cost advantage at small and perhaps medium quantities. This conclusion is not necessarily warranted. Consider the following points:

A. In a *series* of semicustom chips the excess number of components is never larger than the gap between the chips. For example, the bipolar linear series described in this manual consists of nine chips, covering the range from 37 to 630 transistors. Each succeeding chip increases in area by 30%, thus at least 70% of the components are used, otherwise one would used the next smaller chip. Improvement in device design and chip architecture has made it possible to use close to 100% of the components.

- B. The cost of an integrated circuit is not determined by chip area alone. An equally important factor is packaging cost. A 30% higher chip area, for example, will be reduced to a much smaller percentage after assembly.

- C. Because semicustom chips almost always have *some* excess components, changes can be made easily. While this feature is important during the development phase, it is often more welcome during the initial marketing phase to incorporate last minute flaws or customer wishes. It is not uncommon for a chip which had been planned to be converted to full custom to stay in semicustom form for several years.

Copyright 1991, 1992, 1995,1997 Array Design Inc., San Francisco. This manual is protected by copyright law, but may be reproduced for the purpose of design or teaching. Any such reproduction must include this legal notice.

www.arraydesign.com

Blank page.

## How These Chips Are Made

Semiconductors, as the name indicates, are a group of materials located in between conductors and insulators. There are only a few of them, mainly the elements silicon and germanium and some compounds such as gallium-arsenide.

A semiconductor is, however, not just a poor conductor or poor insulator. In contrast to resistive materials (such as carbon) it conducts electricity only if other atoms are also present. By itself it is an insulator.

Let's take the example of silicon. It is element number 14 in the periodic table. Its 14 electrons are in three distinct orbits: two in the first, eight in the second and four in the third. It is the outermost orbit which determines the *valence* of an element. Silicon, therefore, has a valence of four.

In pure form (and in a temperature range around room temperature) all four outer electrons cling tightly to the silicon atom. Thus, unlike in conductors where the outermost electrons will jump from atom to atom under the influence of an electric field, the electrons of pure silicon stay in place and very little electric current can flow.

If we insert an atom with a different valence into silicon, however, things change. If this atom has an additional electron (a valence of five), four of the five electrons in its outermost shell are tied up with the four electrons of the silicon atoms (providing the cohesive force); the fifth electron is unused and is free to travel. In order for this electron to travel easily however, the silicon must be a crystal, i.e. all silicon atoms must be aligned in perfect order.

Elements with a valence of five are, among others, phosphorus, arsenic and antimony. If these elements are inserted, silicon becomes *n-type* (n denoting the negative charge of the excess electrons). The more heavily silicon is "doped" with these elements, the more conductive it becomes. Even at the maximum doping level there are comparatively few dopant atoms, fewer than one for every 10,000 silicon atoms.

Similarly we can also introduce elements with a valence of three into silicon, such as boron or gallium. When we do that there is an electron missing, forming a positive charge. This charge, or *hole*, also moves under the influence of electric charge, albeit a bit more

awkwardly. Such a semiconductor is said to be *p-type*.

How do we insert these dopants into silicon? Diffusion is the most common method. Atoms do not stay in place, they move, or diffuse. In gasses diffusion is rapid, in liquids quite slow and in solids, at room temperature, imperceptibly minute. If we heat a solid, however, the speed of diffusion increases. If we heat silicon to red-heat (about 1200°C) a gas on the outside diffuses into the surface of the solid. Even at this temperature it may take an hour or so to reach a depth of a few micrometers (microns).

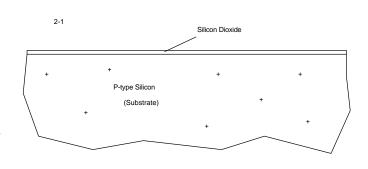

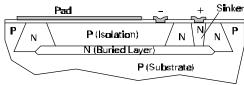

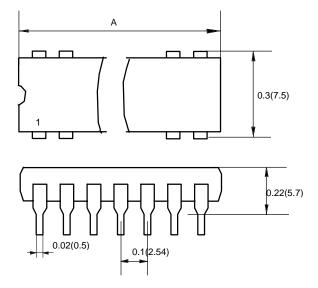

The starting point for our integrated circuit is shown in figure 2-1. It is a single-crystal wafer about 0.02 inches (0.5mm) thick, doped p-type. Silicon covers itself with an oxide layer when exposed to air. This oxide (silicondioxide to be precise, one form of glass) plays a crucial role in the fabrication and operation of an

integrated circuit. For this reason it is grown on purpose under controlled conditions.

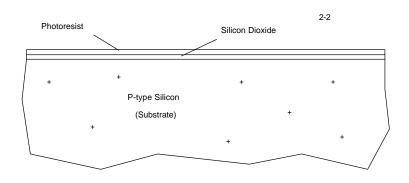

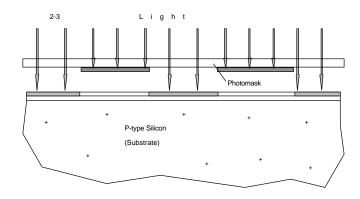

Next (figure 2-2) we spread a thin layer of photoresist on top of the oxide. This is the same kind of light-sensitive emulsion as is used on a photographic film. When the photoresist is dry it is exposed to light through a mask. The mask - a plate of glass - contains the first pattern for the integrated circuit. This can either be a contact print (where the mask is laid on top of the wafer), or a projection exposure (with the mask in close proximity but not touching the wafer). The dark patterns on the mask prevent the light from reaching the photoresist; in the remaining area the photoresist is exposed, developed and subsequently removed.

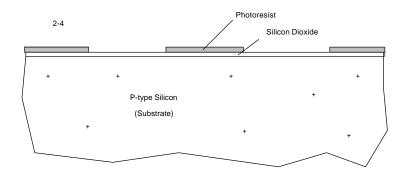

We now have the pattern of the mask directly on the wafer (figure 2-4). With an etchant we can remove the silicondioxide where it is not protected by the photoresist. The etchant only attacks the oxide; etching action stops at the silicon. After the etching step the photoresist is removed.

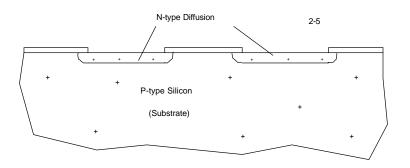

Next (figure 2-5) we expose the wafer to a gas at high temperature. The gas contains n-type dopant, which diffuses into the silicon. The concentration of dopants in these pockets is as high as we can make it, to result in the lowest possible resistance.

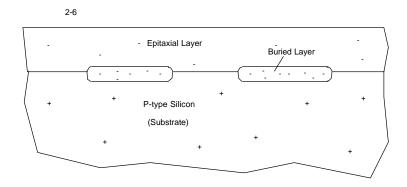

After this first diffusion we remove the remaining silicon-dioxide and grow an additional layer of silicon (figure 2-6). Called the *epitaxial layer*, it is lightly doped n-type and its silicon and dopant atoms continue in the perfect crystal structure of the substrate. Since the highly-doped n-layer is now located underneath

the epitaxial layer, it is named the buried layer.

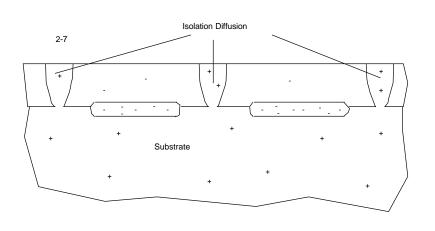

The growth of the epitaxial layer followed by the isolation diffusion. Figure 2-7 shows the result (for this and all following diffusions we have omitted showing the detailed steps applying the photoresist, mask exposure and oxide etchina). isolation diffusion is a deep one, it penetrates the epitaxial layer. The

concentration of p-type dopants in these areas is higher than the previous n-type level, so that the region is converted from n to p-type.

Notice that we now have two n-type pockets, entirely surrounded by p-type silicon. As long as these pockets are held at a voltage more positive than that of the substrate (which is also connected to the regions created by the isolation diffusion), its boundaries form a reverse-biased diode, with little or no current flowing. Thus, these regions are electrically separated by *junction isolation*.

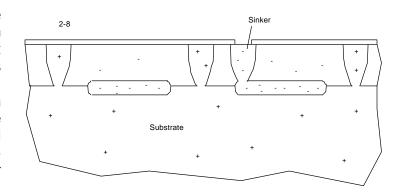

After each diffusion the oxide layer is regrown, so that we can pattern it in new areas. The next diffusion (figure 2-8) gives us access to the buried layer. Called the *sinker* it provides a low-resistance path through the epitaxial layer. The sinker and buried layer provide a low-resistance path for the collector of the NPN transistor.

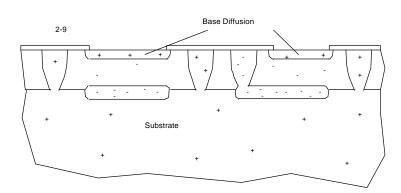

For the center layer of the NPN transistor, the base, we diffuse P-type impurities to a depth of about 1 micron.

Since a doped semiconductor has a certain resistance (which varies inversely with the dopant concentration), it can be shaped into a resistor. The base diffusion is the layer best suited for this job.

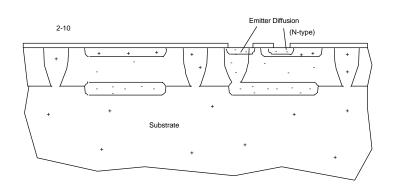

The last diffusion in the process forms the emitters of the NPN transistors (figure 2-10). It is also used to lower the collector access resistance even further. The difference in depth between the base and emitter diffusions forms the actual base of the NPN transistor. For high current gain it must have a very fine and well-controlled width (on the order of 0.1um).

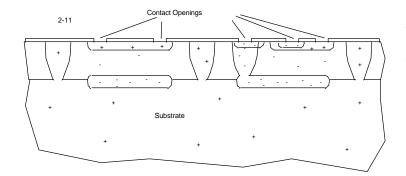

After the diffusions are complete we regrow the oxide layer and pattern the contact openings (figure 2-11).

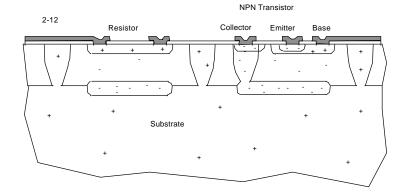

The wafer is finished at this point by depositing a thin (1um) aluminum layer over the entire surface, patterning and etching it so that it forms the interconnection pattern (figure 2-12). The wafer is then protected with a thick oxide layer, which is removed only in the bonding pad areas.

Copyright 1991 to 2000, Array Design Inc., San Francisco. This manual is protected by copyright law, but may be reproduced for the purpose of design or teaching. Any such reproduction must include this legal notice.

www.arraydesign.com

## **Devices**

## Statistical Distributions

Nothing we attempt to do is ever perfect. We aim at a goal and we are certain to miss it. If we are good at it (or lucky) the error is so minute that we can hardly measure it, but there is always an error.

Let's take the case of making an ordinary resistor. You deposit some resistive material (say carbon) on a ceramic tube and measure the resistance. You aimed at 100 Ohms and got 110. So you adjust your machine and try again. The result is 99 Ohms. You are satisfied and start production. The next day the line voltage is a little high and your resistors are running 95 Ohms. You adjust for it and the following day you measure 103 Ohms. Then the barometer changes and the resistance walks up to 104 Ohms. And so on.

If you plot your measurements day in and day out you are more than likely to find a Gaussian distribution. With diligence you will most often get a measurement of 100 Ohms (within the measurement accuracy), followed by ever smaller quantities with higher and lower resistances. The Gaussian distribution is a handy tool to describe variation.

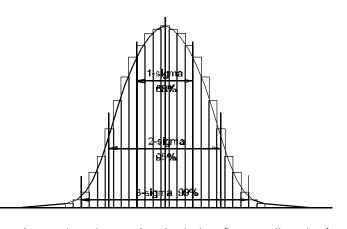

The area under the curve contains all the

measurements. Most scientific calculators can determine sigma, the deviation (in one direction);  $\pm$  sigma (in both directions) contains 68.3% of all measurements. If we double this value (2-sigma) we get a deviation which contains 95.4% of all measurements; by tripling it (3-sigma) we get the deviation for 99.7% of all measurements. It is this 3-sigma limit which is most commonly used in IC design.

All parameters in an IC have a distribution, though not all of them are Gaussian. For example, hFE has a skewed distribution (more values toward the high end), but the error is small enough to include it in the Gaussian family.

A discrete resistor can be tested after fabrication. If we find a resistor with a value outside certain limits (say 3-sigma), we can throw it away or put it in a different bin. The distribution of the final resistors is then truncated: there will be no values outside 3-sigma.

In an IC we cannot test each component before use, we have to accept what is there. Thus, even if we design a circuit to 3-sigma limits, a small percentage of the parameters will be outside the limits and must be eliminated by testing the entire circuit. For this reason the 3-sigma limits given in this chapter should be accepted as the minimum standard. Be also aware that these percentages multiply. If you have 10 parameters which are critical, the total percentage of circuits inside the 3-sigma limits is not 99.7% but 97% (0.997<sup>10</sup>).

Here is the entire listing of tolerance and the resulting percentages:

| <u>Tolerance</u> | <u>Pass</u> | <u>Fail</u> |

|------------------|-------------|-------------|

| 1-sigma          | 68.26%      | 31.75%      |

| 2-sigma          | 95.44%      | 4.56%       |

| 3-sigma          | 99.73%      | 0.27%       |

| 4-sigma          | 99.994%     | 0.006%      |

| 5-sigma          | 99.99994%   | 0.00006%    |

#### **Parameter Correlation**

The overwhelming majority of IC parameters are independent of each other. For example, there is no correlation at all between the hFE of an NPN transistor and that of a PNP transistor. The first one is determined mostly by the difference in thickness between the base and emitter diffusions, the second by the distance between two base regions.

Four parameters, however, show some relationships:

- The higher the NPN hFE, the lower the current of the base pinch resistor.

- The lower the resistor value, the lower the Zener voltage.

### Isolation

If you follow two simple rules, all components in the 700 series chips will be properly isolated:

- 1. Connect the substrate to the most negative voltage. The connection to the substrate is the MNUS metal run around the entire chip.

- 2. Connect at least one + V contact to the most positive voltage. This is the connection to the (epitaxial) N-layer surrounding all resistors.

If you have multiple supply voltages and it is possible for any one to be the most positive at different times, connect a Schottky diode from the N-layer to each supply (cathode at the N-layer). In this way it is always the highest supply which will bias the N-layer. This, however, has some limitations at high frequencies.

## **NPN Transistor**

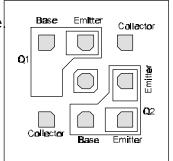

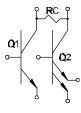

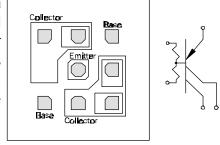

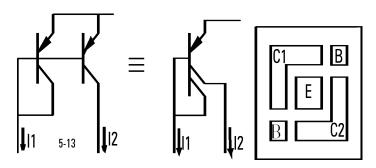

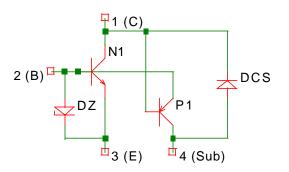

All the 700 Series chips contain a transistor which is both NPN and PNP; you decide which it is to be

Used as an NPN, the structure contains two separate bases, a total of 3 emitters and two collector contacts. Thus, you can connect it as:

- two NPN transistors with a common collector,

- one NPN transistor with 1, 2 or 3 emitters (connect the bases together for three emitters, or two in different bases), or

- one NPN transistor and one Zener diode.

The multiple emitters can be used to create current ratios or to increase the current handling capability.

The two horizontal emitters match best since they have identical orientation.

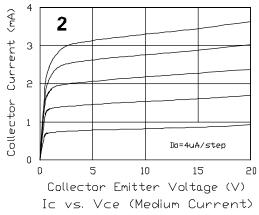

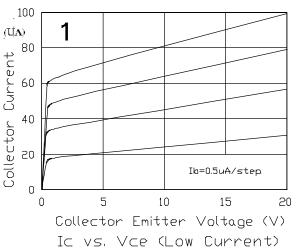

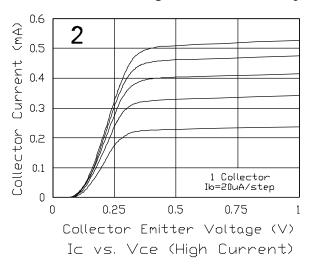

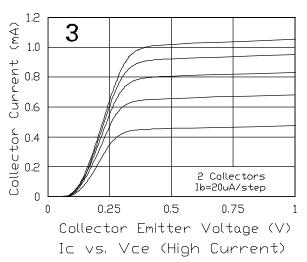

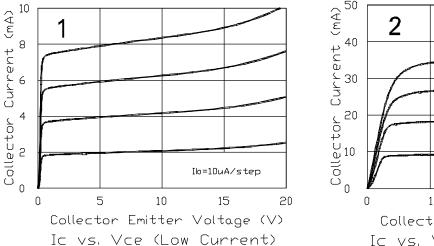

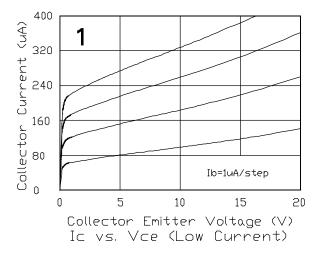

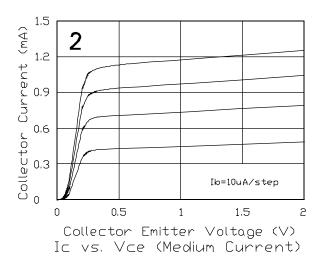

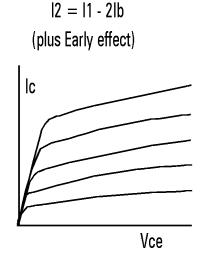

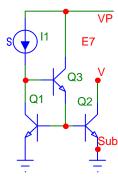

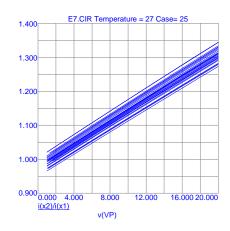

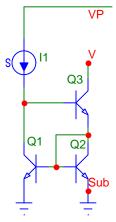

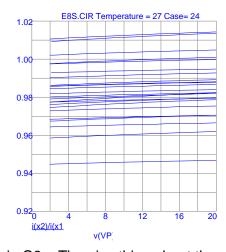

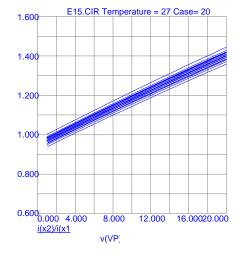

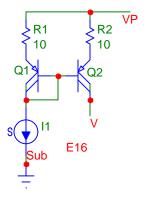

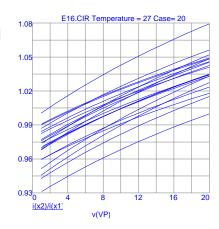

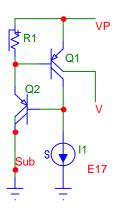

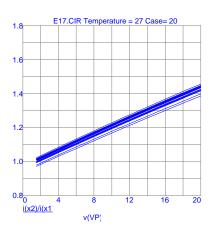

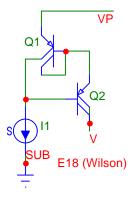

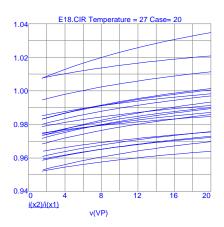

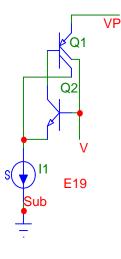

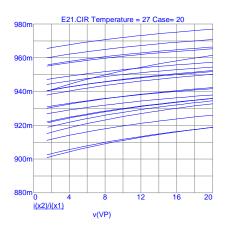

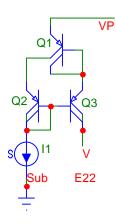

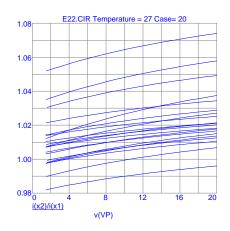

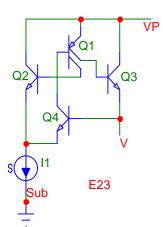

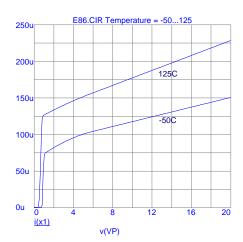

**Graphs 1 and 2** Notice the Early effect. The lines slope upward with increasing voltage, especially close to 20 Volts Vce.

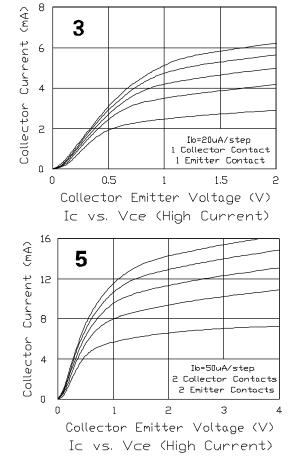

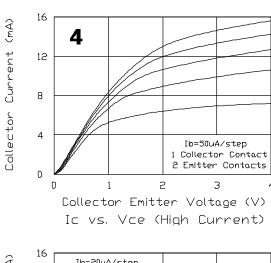

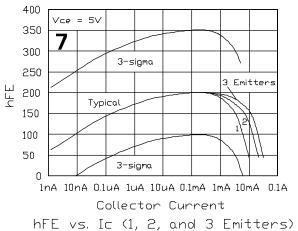

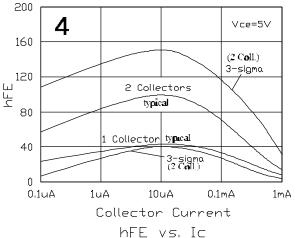

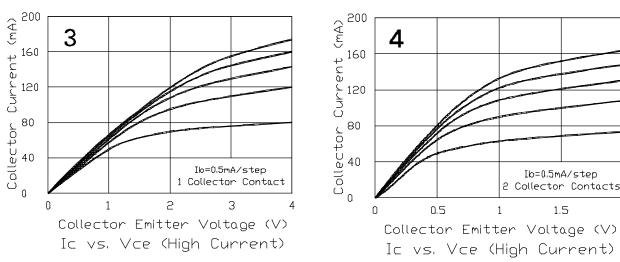

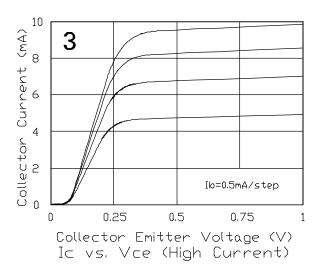

**Graphs 3 to 6** Using both collector contacts results in a lower saturation voltage; additional emitters increase the upper current range (i.e the gain at high current).

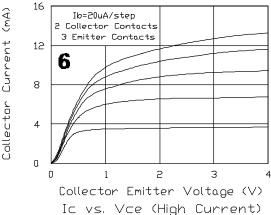

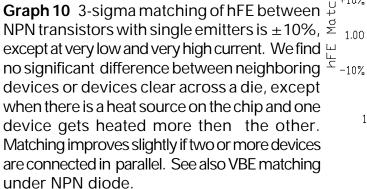

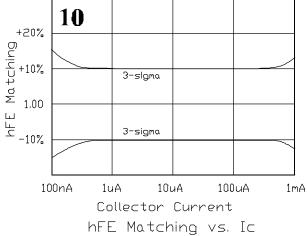

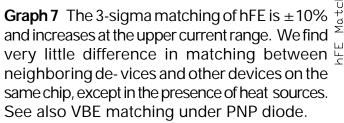

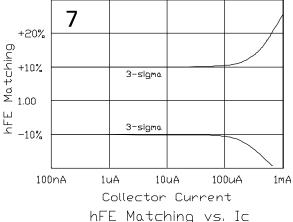

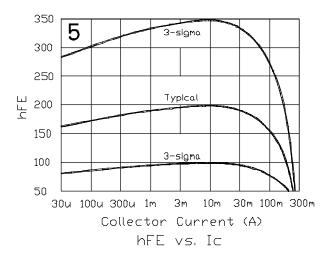

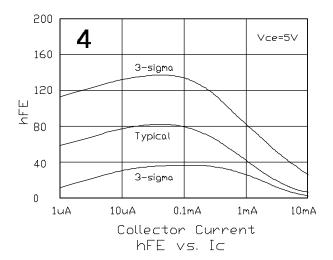

**Graph 7** hFE vs collector current. At about 300uA the nominal hFE is 200, with a 3-sigma range of 100 to 350. hFE drops off both at low and high current. You can extend the upper current range by using 2 or 3 emitters.

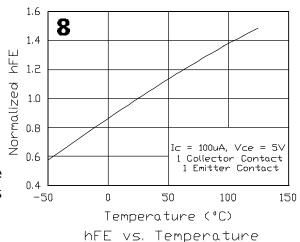

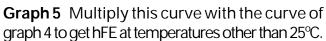

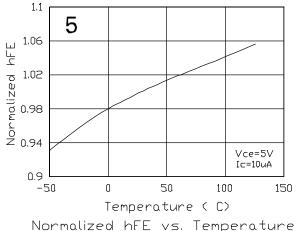

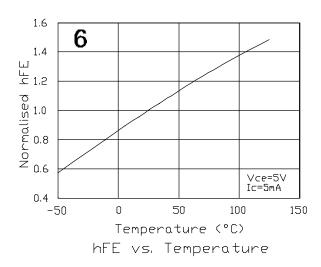

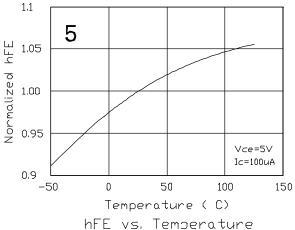

**Graph 8** Normalized hFE is multiplied with the hFE of graph 7 to get the hFE at temperatures other than 25°C.

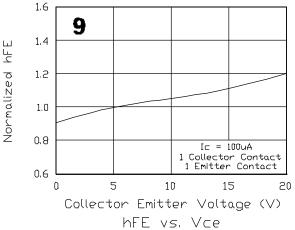

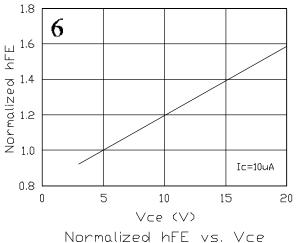

**Graph 9** Normalized hFE is again multiplied with the hFE of graph 7. This graph shows the Early effect.

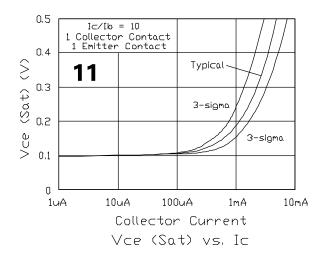

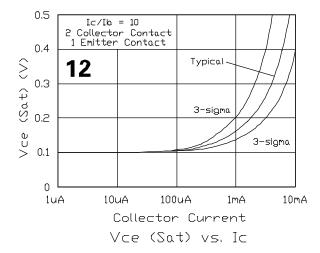

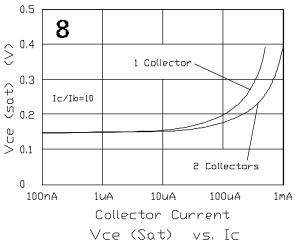

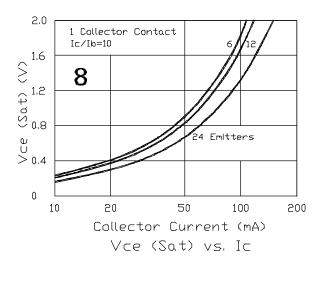

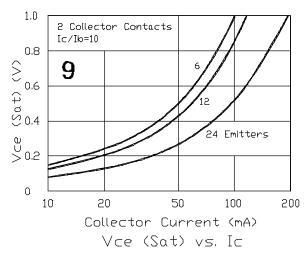

**Graphs 11 and 12** Using 2 collector contacts reduces the saturation voltage in the upper current range.

CAUTION: When you use this device as a dual NPN transistor and one of the two transistors saturates, a low-gain PNP transistor is created between the two. This stray device works as follows: the base of the saturating NPN becomes the emitter (with a potential of about 0.65 Volts); the collector of both NPN transistors is the base (in saturation it is near ground); the base of the second NPN transistor now acts as the collector. The gain of this device is about 0.15.

The effect of this stray PNP is only noticed if the base of the second NPN transistor is open and the base of a third NPN is also connected to this point. In this case the collector current of the stray PNP flows out of the base of the second NPN and turns on the third.

When using a dual NPN and one of the two transistors may saturate, you should take two precautions: 1) Ground the center contact (the PNP emitter); this reduces the gain of the stray PNP to about 0.02. 2) Provide a leakage path from the base of the non-saturating NPN to ground (e.g. a base or epi pinch resistor or a current sink).

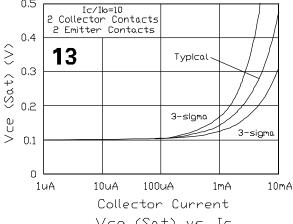

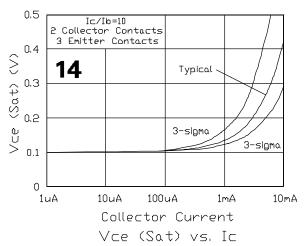

**Graphs 13 and 14** Saturation voltage with 2 and 3 emitters. Unless the transistor is operated at low current levels only, connect both collector contacts.

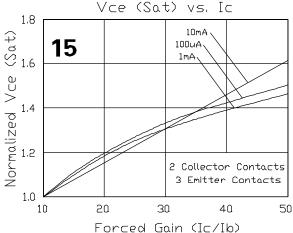

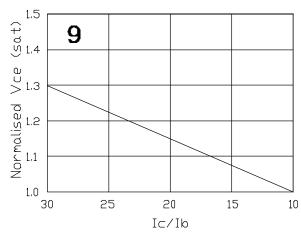

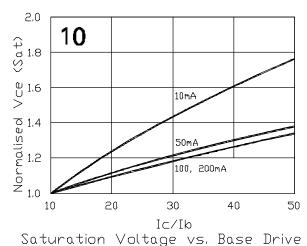

**Graph 15** Graphs 11 to 14 are shown with a base current which is 10% of the collector current. If you don't want to drive the transistor that hard, use graph 15 as a multiplier for saturation voltage.

Saturation Voltage vs. Base Drive

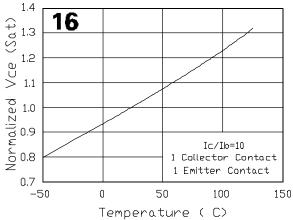

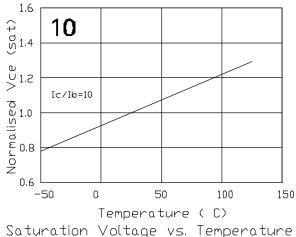

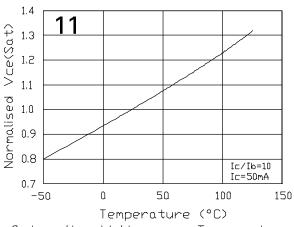

**Graph 16** multiplies the saturation voltage for temperatures other than 25°C.

Saturation Voltage vs. Temperature

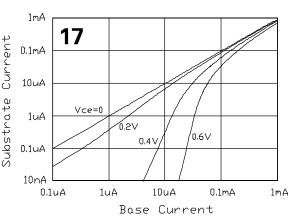

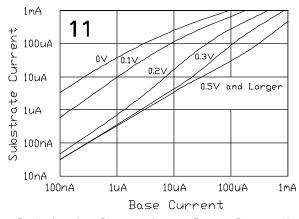

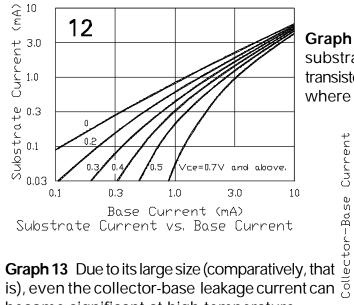

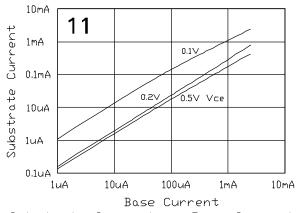

Graph 17 When the NPN transistor saturates a rather substantial substrate current flows. This current is collected at the edge of the chip by the -V run. A large total substrate current (greater than about 10mA) could, conceivably, for-ward bias some junctions in its path, especially if its source is in the center of the chip.

The substrate current is directly dependent on the amount of base current and is a strong function on how low you let the collector-emitter voltage drop.

Substrate Current vs. Base Current

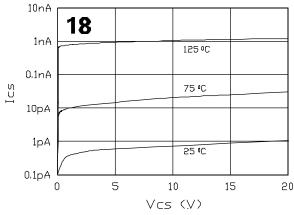

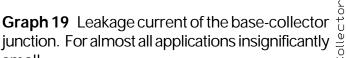

Collector Substrate Leakage Current

small.

**Graph 18** The junction isolating the NPN transistor from the substrate has some leakage current, which can be a factor at the upper temperature range in low- current application.

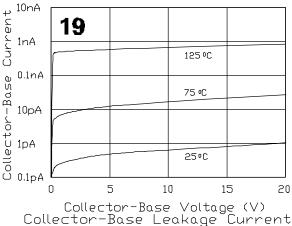

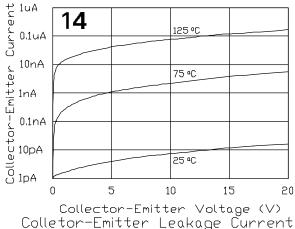

**Graph 20** Leakage current from collector to emitter. This is the collector-base leakage current multiplied by the hFE. At high temperature this leakage current becomes significant in low-current applications.

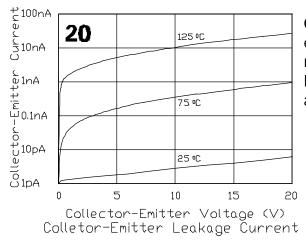

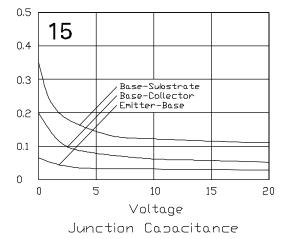

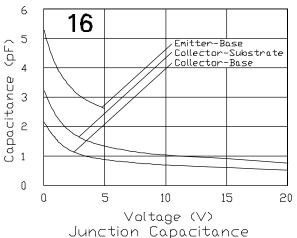

**Graph 21** Capacitance of the three junctions vs applied (reverse) voltage. These capacitances are considerably smaller than the capacitances in other 20 Volt semicustom chips, owing to the small (4 micron) dimension used. Band- width (ft) is approx. 800 MHz.

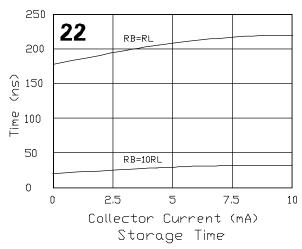

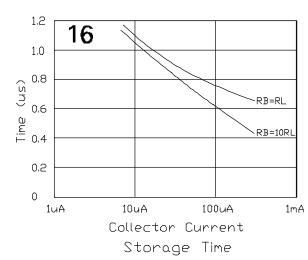

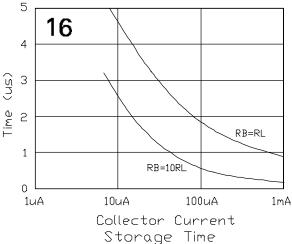

**Graph 22** Storage time - the time it takes for the transistor to come out of saturation. If you have a high impedance at the base it takes far more time for the transistor to turn off than with a path (resistor or current sink) which can dis-charge the base. Also, the higher the ratio of Ic/Ib, the faster the transistor will turn off.

## NPN Transistor (continued), NPN Diode

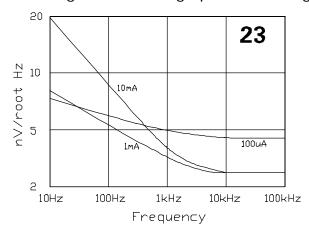

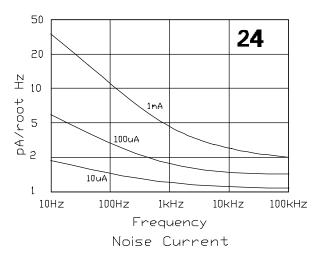

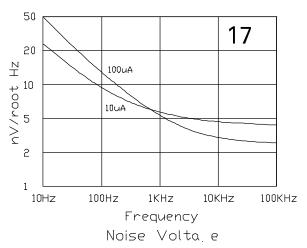

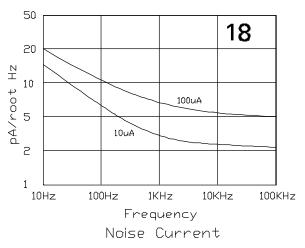

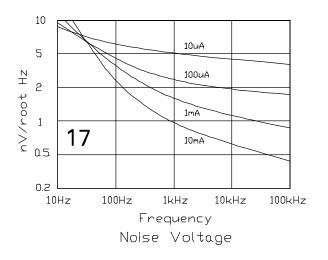

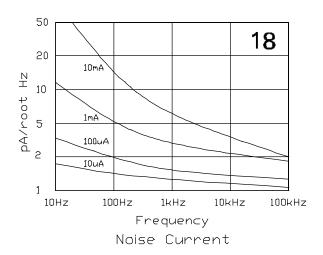

**Graphs 23 and 24** Noise is plotted in nano-Volts or pico-Amperes per root-Hertz. Also compare these figures with the graphs for the large NPN transistor.

#### **NPN Diode**

There are no pure diodes in most ICs, you make them either out of an NPN or a PNP transistor. In the NPN transistor you connect base and collector terminals together (which becomes the anode); the other terminal is the emitter. This diode has a low reverse breakdown voltage (that of the Zener diode, about 5.9 Volts), but is very predictable in the forward direction.

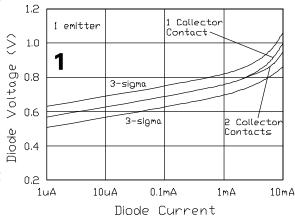

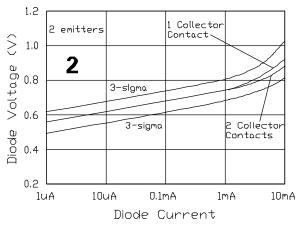

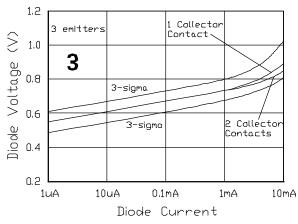

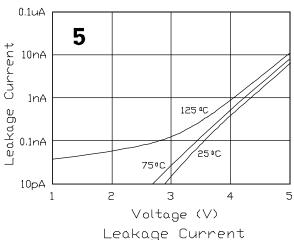

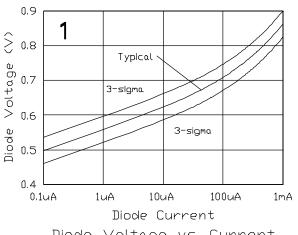

**Graphs 1 to 3** The forward voltage drop is highly linear over about 8 decades of current, up to at least 1mA. It follows the equation

Delta-VBE = (kT/q)ln[(A2l1)/(A1l2)]

(see also chapter 5). At room temperature kt/q > amounts to 26mV, so a ten-fold increase in current will increase VBE by 60mV. Going from 1 to 2 = emitters re-duces VBE by 18mV. Note that, for best performance at the upper current range, you need to connect both collector contacts.

Diode Voltage vs. Current (1 emitter)

#### NPN Diode, Zener Diode

Diode Voltage vs. Current (2 emitters)

Diode Voltage vs. Current (3 emitters)

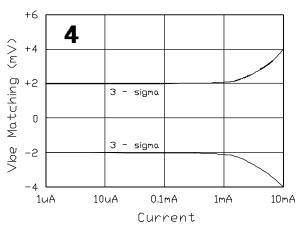

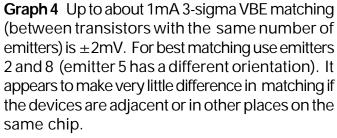

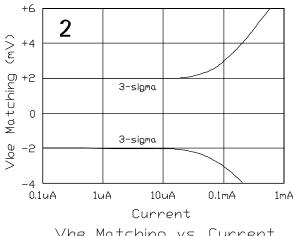

Vbe Matching vs. Current

## **Zener Diode**

The connection for the Zener diode is identical to that of the NPN diode (you should not leave the collector floating). 3-sigma voltage spread is 5.6 to 6.1 Volts, with a nominal breakdown of 5.9 Volts. Temperature coefficient is approx +200ppm/°C.

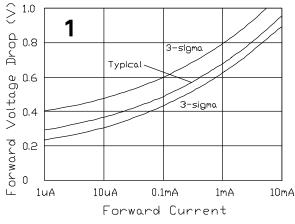

**Graph 5** Leakage current of the base-emitter junction.

## Zener Diode (continued), Schottky Diode

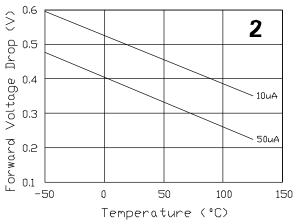

**Graph 6** The slope of the Zener diode breakdown curve.

## **Schottky Diode**

Some transistors in the 700 Series carry a Schottky diode instead of a second base. A Schottky diode is simply the junction between the aluminum and the (high resistivity) epi layer. Compared to silicon p-n junctions, the Schottky diode produces a lower forward voltage drop.

You can use this transistor as:

- a Schottky diode (ignoring the base and two emitters)

- a one or two emitter NPN transistor (ignoring the Schottky diode)

- a Schottky-clamped NPN transistor (connecting the aluminum of the Schottky diode to the base). Such a transistor does not saturate and thus turns off more rapidly.

Forward Voltage Drop vs. Current

**Graph 1** Forward voltage drop vs current. Note that this Schottky diode is de-signed to operate at low current only (about 50uA max).

## **Schottky Diode (continued)**

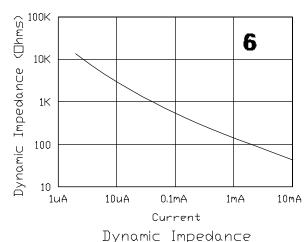

**Graph 2** Voltage drop at 10 and 50uA vs. temperature.

Forward Voltage Drop vs. Temperature

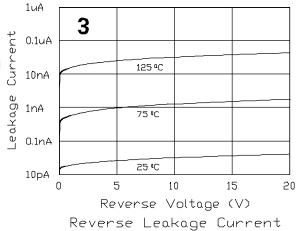

**Graph 3** Beware that the Schottky diode has a higher leakage current than p-n junctions.

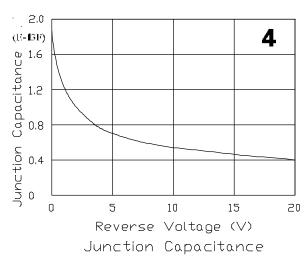

**Graph 4** Junction capacitance vs applied (reverse) voltage.

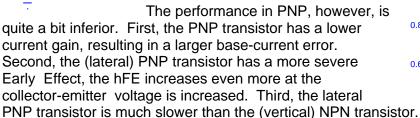

#### **PNP Transistor**

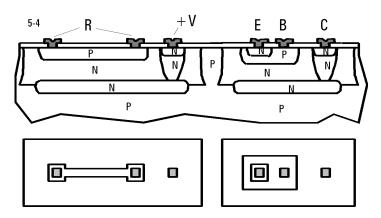

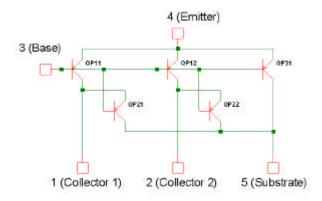

The structure that houses NPN devices can also be used as a PNP transistor. The center p-type region, unused in the NPN mode, becomes the PNP emitter. It emits current radially or laterally through the base (the epi layer) and this current is collected by two identical L-shaped regions (the NPN bases). Each collector gets half the current. The NPN emitters are ignored.

Since the base is fairly wide, the lateral PNP transistor has a lower current gain than the NPN device and its speed is inferior (ft is approx. 30MHz).

**Graph 1** Notice the Early effect (the upward sloping curves).

**Graphs 2 and 3** The PNP transistor has a collector offset voltage of about 100mV, below which the saturation voltage cannot fall at any current level.

**Graph 4** There is a significant hFE drop-off above about 100uA. In general, this device is rarely useful above 300uA (i.e. 150uA per collector). Both collectors are always active; you cannot

simply ignore one collector. If you don't need to split the current into two equal parts, connect both collectors together.

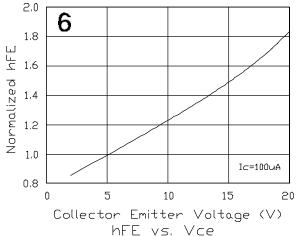

**Graph 6** Multiply this curve with the curves of graphs 4 and 5 to get hFE at voltages other than 5 Volts. It depicts the Early effect.

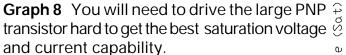

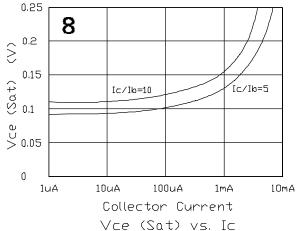

**Graph 8** Saturation voltage vs collector current. You can, of course connect PNP transistors in parallel to get lower saturation voltage and higher current capability.

○ 0.3

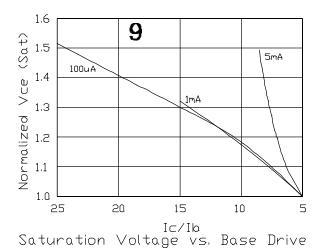

Saturation Voltage vs. Base Drive

Graph 9 Multiply this curve with the curve of graph 8 to get saturation voltage if you use a base current which is less than 10% of the collector current.

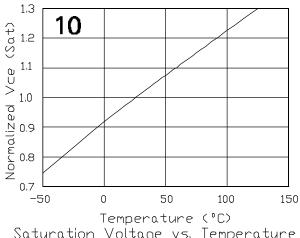

**Graph 10** Multiply this curve with the curve of graph 8 to get the saturation voltage at temperatures other than 25°C.

Substrate Current vs. Base Current

**Graph 11** The PNP transistor always has some current flowing to the substrate, a current which is proportional to its base current. When any of its collectors saturate this flow of current becomes

substantial. It is collected at the edge of the chip by the -V run. A large substrate current (greater than about 10mA) could, conceivably, forward bias some junctions in its path, especially if its source is in the center of the chip. So, be careful about letting too many PNP transistors saturate with a high base current. You can measure this current in the substrate pins of the kit-parts.

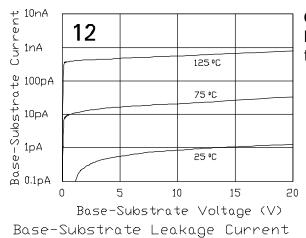

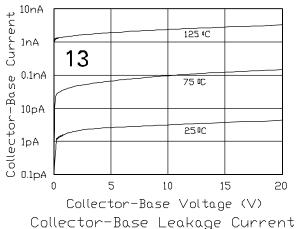

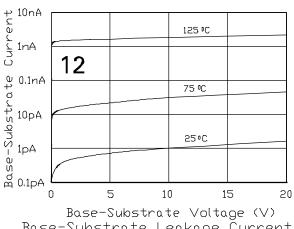

**Graph 12** Leakage current from base (the epitaxial layer) to substrate. Can be significant at high temperature with very low base currents.

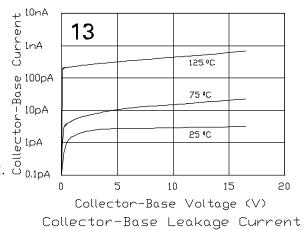

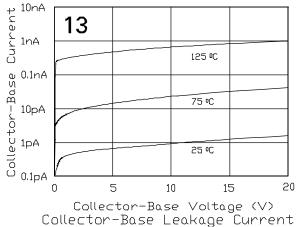

**Graph 13** Collector-base leakage current. Usually too small to worry about.

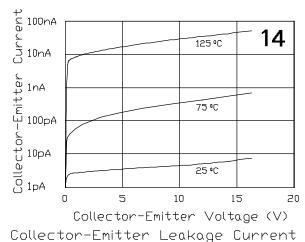

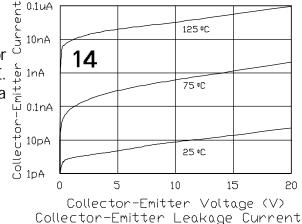

**Graph 14** Leakage current from collector the emitter. This is the collector-base leakage current multiplied by the hFE. At high temperature this leakage current becomes significant in low-current applications.

## PNP Transistor (continued), PNP Diode

Graph 16 Storage time (the time it takes the transistor to turn off after you remove the base signal) vs collector current. You can speed up storage time by providing a path to discharge the base (a resistor or current source) and using a high lc/lb ratio. You should not use lateral PNP transistors for speeds of less than 100nsec, the models lack accuracy at extreme speed.

**Graphs 17 and 18** The lateral PNP transistor is not particularly noted for low noise. Compare this with the noise of the NPN (and particularly the large NPN) transistor.

#### **PNP Diode**

As we noted before, the NPN diode has a low breakdown voltage (the Zener voltage, about 5.9 Volts). If you need a diode with a breakdown voltage of up to 20 Volts, use the PNP transistor, connecting together the collectors and the base.

## PNP Diode (continued), Large NPN Transistor

Graph 1 The current capability of the PNP transistor is limited to about 300uA. Also not that, if you go higher in current, there will be significant substrate cur- rent.

Diode Voltage vs. Current

Graph 2 Matching of VBE (in PNP transistors or diodes) is ±2mV, increasing toward! diodes) is  $\pm 2mV$ , increasing toward the upper  $\frac{\omega}{2}$  -2 current range as the device runs out of current gain.  $\geq$ It appears to make very little difference in matching if the devices are adjacent or in other places on the same chip.

Vbe Matching vs. Current

## Large NPN Transistor

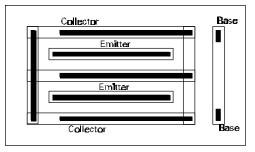

The large NPN transistor, located on the periphery of each chip, consists of 24 emitters, each identical to the emitter of the (small) NPN transistor. There are 12 separate base regions, each containing 2 emitters. All of these emitters and bases are in a single collector region with two opposite contacts.

Bases **Bases** 30 ()Emitters Emitters | Emitters

Connect as many emitters and bases as you like (however, if an emitter is used, the base

containing it must be connected too). In this way you can:

- create current ratios between 1 and 24,

- get an increased current handling capability (up to 200mA) and

- create a multiple base / multiple emitter device with a common collector.

**Graphs 1 and 2** The large NPN transistor has the same Early effect (the in-creased current gain toward higher collector-emitter voltage) as the (small) NPN transistor.

**Graphs 3 and 4** Connecting both collector contacts results in a lower saturation voltage. You can, of course, connect a second large NPN transistor in parallel, but be aware of wide metal runs necessary for the collector and emitter leads.

#### A Note on Metal Widths

If you exceed a certain current density in the aluminum, you can cause migration or even melting. We use as a safe upper limit  $4x10^5$ Amperes/cm2, which corresponds to 4 mA per micron width. The normal (and minimum) metal width is 4 microns, so you can run 16mA safely through the smallest metal run.

## **Large NPN Transistor (continued)**

To avail yourself of the 200mA capability of the large NPN transistor you need to use a metal width of 50 microns.

You should also be aware of the resistance of the aluminum layer which, although small, can add up to significance in a long, narrow run. The nominal resistance of the aluminum is 40mOhms/square, with an upper (3-sigma) limit of 80mOhms/square. To calculate the resistance of a run you simply divide its length by its width to get the number of squares. A 4-micron wide, 80-micron long run, for example, has 20 squares, amounting to 0.8 Ohms nominal.

**Graphs 5 and 6** The current gain drops off long before you reach 200mA, but is still high enough to be useful. Consider a compound transistor (see chapter 5) if you need a higher current gain. The curve of graph 6 is multiplied with graph 5 to get hFE at temperatures other than 25°C.

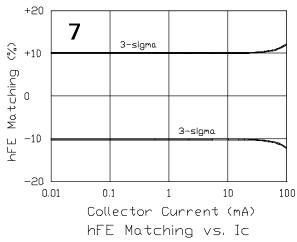

**Graph 7** Matching of hFE for single emitter or current ratios to single emitters. The more emitters you match (e.g. 12:12) the better the matching.

## **Large NPN Transistor (continued)**

**Graphs 8 to 11** Current handling depends strictly on the number of emitters you use. Note the difference in saturation voltage between one and two collector contacts. If you drive the base with less than 10% of the collector current, use graph 10. Graph 11 multiplies the other graphs for temperatures other than 25°C.

Saturation Voltage vs. Temperature

## Large NPN Transistor (continued)

**Graph 12** In saturation there is a substantial substrate current. That is why the large NPN transistors are located close to the edge of the chip where the substrate current is collected.

become significant at high temperature.

**Graph 14** Don't ignore the collector-emitter leakage current of the large NPN transistor, especially at high temperatures. If you provide a path between base and emitter, it will drop to the level of the collector-base current.

## Large NPN Transistor (continued), Large PNP Transistor

**Graph 16** Junction capacitances vs applied (reverse) voltage. Larger than those of the small device. The large NPN transistor has an ft of about 400MHz.

**Graphs 17 and 18** The large NPN transistor, operated at the current levels of the (small) NPN transistor, makes an excellent low-noise device.

## **Large PNP Transistor**

The large PNP transistor uses the same layers as the (small) PNP transistor, but there are two long emitters, fully enclosed by the collector. This device is capable of carrying a larger current (6mA), though it is still limited in frequency response and current gain.

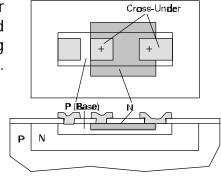

The two emitters are connected together and all three of the parallel collector-metal lines must be used. The transistor has an optional cross-under in the base connection.

**Graphs 1 to 4** The large PNP transistor has the same Early effect as the smaller device and, at about 200uA, its hFE starts to drop off. Up to about 6mA the gain is still high enough to be used in a compound transistor connection (see chapter 5) together with the large NPN transistor or as an emitter follower in a class B output stage.

**Graph 5** Multiply this curve with graph 4 to get hFE at temperatures other than 25oC.

**Graph 6** Multiply this curve with graphs 4 and 5 to get hFE at collector-emitter voltages other than 5 Volts. This graph depicts the Early effect.

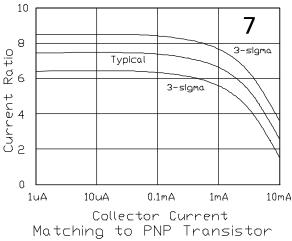

**Graph 7** You can count on some fixed current ratio between the large and the small PNP transistors (about 7.5), though its accuracy is not as good as that between identical devices.

Graphs 9 and 10 These graphs work together (as multipliers) with graph 8.

Saturation Voltage vs. Temperature

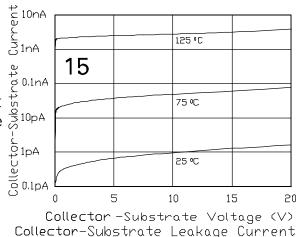

**Graph 11** The large PNP transistor creates a substantial substrate current, especially when it saturates. That is the reason we located it near the edge of the chip, where this current can be collected by the -V trace.

Substrate Current vs. Base Current

Graph 12 There is leakage current between the base (the epitaxial layer) and the substrate, especially at high temperature. Usually too small to matter, unless you operate the device with very low base currents.

Base-Substrate Leakage Current

**Graph 13** Leakage current between collector and base. Usually no bother, un-less you run the transistor below 100nA.

**Graph 14** The leakage current between collector and emitter is that of graph 13, multiplied by hFE. You can avoid this multiplication by providing a path between emitter and base.

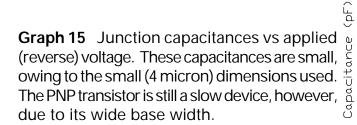

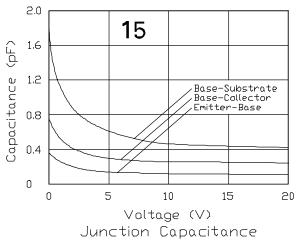

**Graph 15** Capacitance of the three junctions vs applied (reverse) voltage.

Graph 16 The large PNP transistor, as is its smaller counterpart, is not a fast device. You can speed up turn-off somewhat by providing a

discharge path for the base (a resistor or current source).

# **Junction Capacitor**

Underneath some of the pads there are structures which utilize the relatively large capacitance between the isolation diffusion and buried layer (both of these layers have a high doping concentration). Minimum breakdown voltage is 9 Volts, which limits their use to low-voltage

nodes. The pad above can still be used, it is isolated from the capacitor by the oxide layer.

Since this is a reverse-biased junction, one terminal must be consistently more positive than the other.

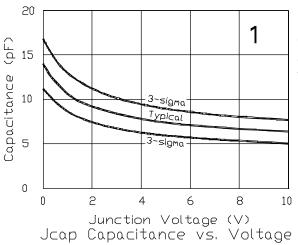

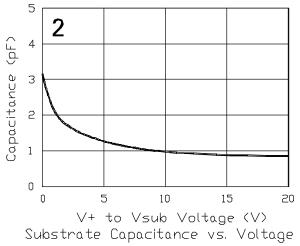

**Graph 1** The capacitance of a junction is voltage dependent. You get the highest capacitance at 0 Volts.

**Graph 2** There is also a stray capacitance between the positive terminal and the substrate.

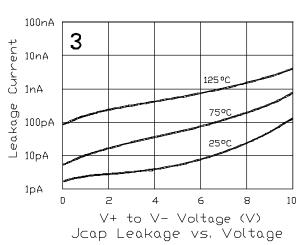

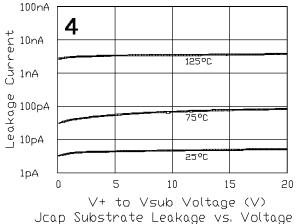

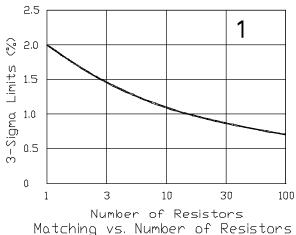

**Graph 3** Leakage current between the two capacitor terminals.

# Junction Capacitor (continued), Resistor

**Graph 4** Leakage between the positive terminal and the substrate.

**Graph 5** The temperature coefficient of the capacitor varies with the voltage across it.

#### Resistor

There is just one resistor value in the 700 Series: 750 Ohms. We chose this approach because the matching between resistors with different geometries is far inferior. You can make a large number of different resistor values by connecting these devices in series and parallel.

The absolute-value (3-sigma) variation for the resistor is  $\pm 20\%$  (600 to 900 Ohms).

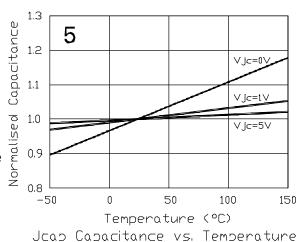

**Graph 1** Two resistors match within 2%. The more resistors you use, the bet- ter the matching gets.

700 Series Manual 3-30

## **Resistor (continued)**

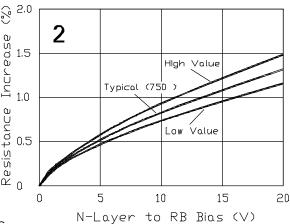

**Graph 2** All resistors are located in a common § <sup>2.0</sup> island (the epitaxial layer), which is connected to the most positive voltage. The voltage between the  $\overset{\vec{N}}{\circ}$  1.5 resistor and the island reduces in effect the resistor and the island reduces in effect the  $\frac{\zeta}{\zeta}$  thickness of the resistor (due to the depletion layer),  $\frac{\zeta}{\zeta}$ so there is a small change in resistance. If possible, therefore, matching resistors should be located at the same DC potential.

High Value: A resistor running close to the maximum of 900 Ohms. Low Value: A resistor with a value below the nominal, close to 600 Ohms. Resistance Change vs. N-Layer Bias

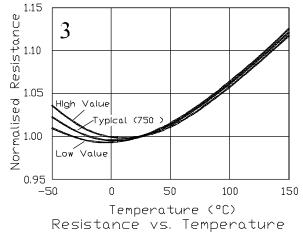

**Graph 3** The value of a diffused resistor changes with temperature and its temperature coefficient is considerably larger than that of even a carbon resistor.

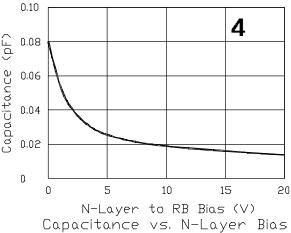

Graph 4 Each resistor has a small capacitance to the island. For a single resistor this results in a -3dB frequency of several GHz. Hardly ever the frequency bottleneck, unless you have a very long string.

#### **Base Pinch Resistor**

There are a few resistors on each chip in which the emitter layer covers most of the base strip. This, together with the applied voltage, "pinches" off the cross-section, so that the resulting resistance is high and non-linear (it is more of a current source). Applied voltage is limited to 5 Volts.

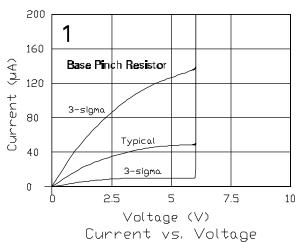

**Graph 1** The variation of a base pinch resistor is large (10 to 150uA). Use it only if you need some current, but the exact amount of current is not very important.

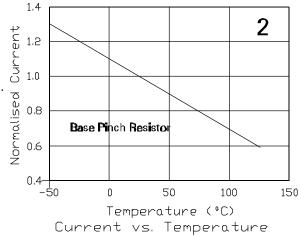

**Graph 2** Temperature coefficient of the current. Multiply this curve with graph 1.

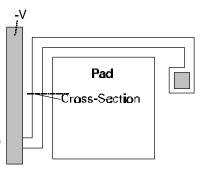

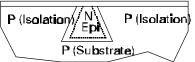

# **Epi Pinch Resistor**

This device, located near a pad, uses the epitaxial layer. But we have made it long and very narrow, so that the resistance is high and the applied voltage (through the depletion layer shown dotted) pinches off the cross-section further. This results in a steady current rather than a resistance.

One terminal of the epi pinch resistor is permanently connected to the substrate; the free terminal, therefore, sinks a current to the most negative voltage.

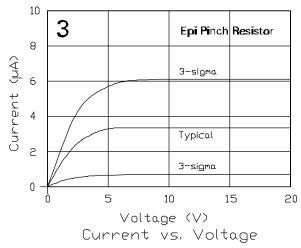

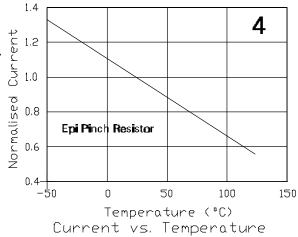

**Graph 3** At about 5 Volts the pinch-off is complete. Between 5 and 20 Volts the epi pinch resistor is a current source. Notice the large variation (1 to 8uA). Use this device only if you need some small current, but the level of the current is not important. Ideal for circuit startup (see chapter 5).

**Graph 4** Temperature coefficient of the current. Multiply this curve with graph 3.

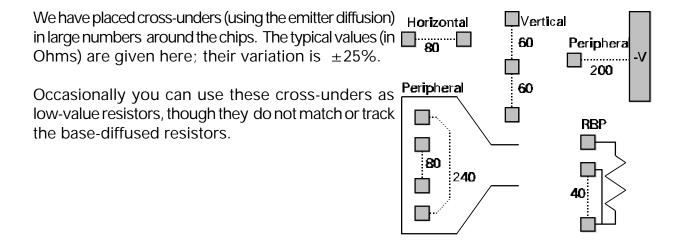

#### **Cross-Unders**

# **Electrostatic Discharge Protection**

Next to most pads there is a small contact box, which leads to a large buried-layer/substrate diode underneath the pad. Although bipolar devices are largely immune to electrostatic discharge, you may increase the amount of protection by covering this box with metal connected to the pad. This adds about 3pF of capacitance to the pad.

This protection diode absorbs negative-going voltage spikes. To reduce positive transients we recommend that you use a wide metal path leading from the pad and let it cross over several resistors and/or cross-unders.

Copyright 1991-2001 Array Design Inc., San Francisco. This manual is protected by copyright law, but may be reproduced for the purpose of design or teaching. Any such reproduction must include this legal notice.

# The 700 Series Chips

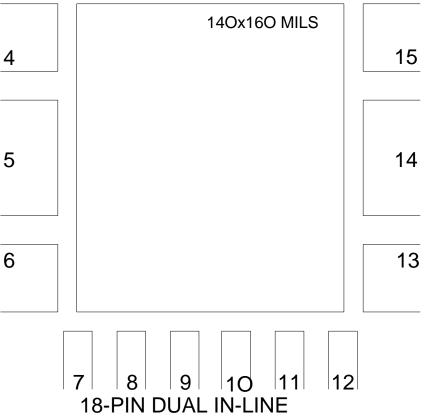

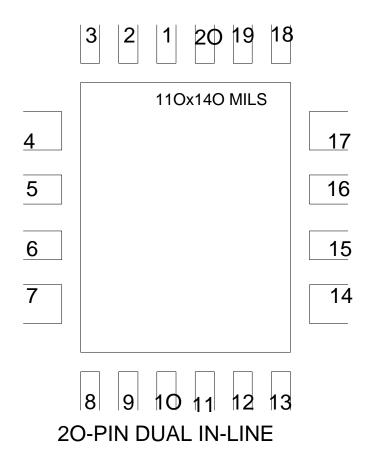

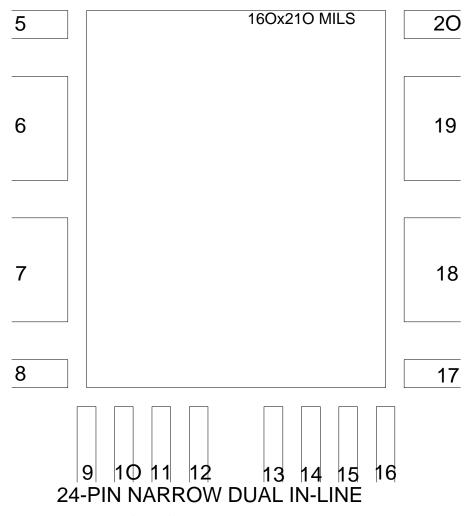

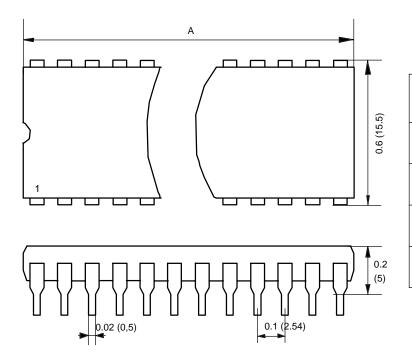

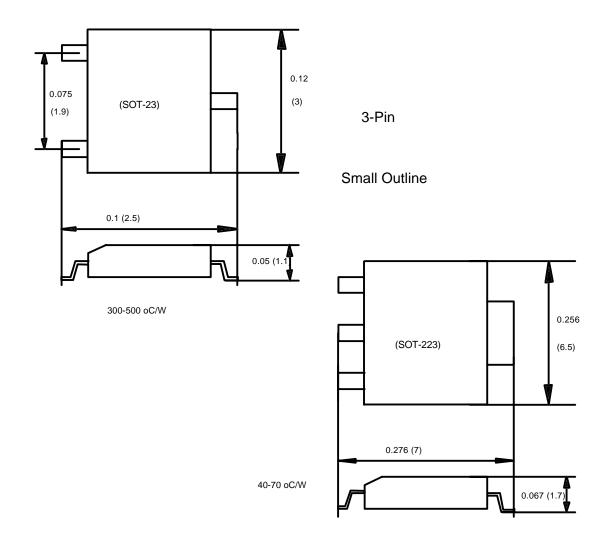

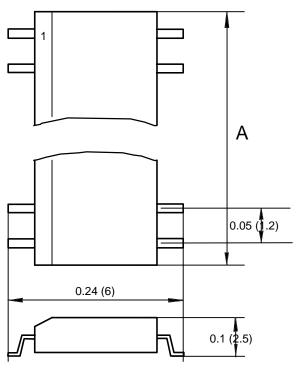

There are nine chips in this series forming a smooth progression in size; except for the smallest one (which was designed to fit into the SOT-23 package) each chip is approximately 30% larger in area than the next smaller one.

| Chip Series           | 710    | 711    | 712    | 713    | 723     | 724      | 734      | 736      | 747      |

|-----------------------|--------|--------|--------|--------|---------|----------|----------|----------|----------|

|                       |        |        |        |        |         |          |          |          |          |

| Die Size mils         | 33x33  | 44x40  | 47x53  | 53x66  | 70x66   | 74x79    | 98x79    | 98x106   | 118x119  |

| Die Size square mils  | 1089   | 1760   | 2491   | 3498   | 4620    | 5846     | 7742     | 10388    | 14042    |

| Pads                  | 4      | 8      | 17     | 22     | 25      | 30       | 30       | 41       | 48       |

| NPN/PNP Transistors   | 14     | 22     | 27     | 39     | 60      | 80       | 120      | 180      | 280      |

| Schottky NPN Trans.   | 4      | 6      | 10     | 11     | 12      | 16       | 24       | 36       | 56       |

| Large NPN Transistors | 1      | 1      | 1      | 2      | 3       | 4        | 9        | 5        | 9        |

| Large PNP Transistors | 0      | 1      | 1      | 2      | 3       | 3        | 6        | 4        | 5        |

| Total Transistors     | 19(33) | 30(52) | 39(66) | 54(93) | 78(138) | 103(183) | 159(279) | 225(406) | 350(630) |

| 750 Ohm Resistors     | 122    | 190    | 210    | 411    | 623     | 895      | 1268     | 1798     | 2487     |

| Total Base Resistance | 91k    | 142k   | 157k   | 308k   | 467k    | 671k     | 951k     | 1.34M    | 1.86M    |

| Base Pinch Resistors  | 2      | 2      | 9      | 9      | 7       | 11       | 8        | 14       | 16       |

| Epi Pinch Resistors   | 1      | 1      | 2      | 2      | 2       | 2        | 2        | 2        | 2        |

| Junction Capacitors   | 1      | 2      | 2      | 4      | 7       | 7        | 9        | 12       | 10       |

| Cross-Unders          | 40     | 68     | 70     | 160    | 200     | 300      | 450      | 650      | 950      |

The main features of the 700 Series are:

- All devices use an advanced, small-geometry process, which results both in smaller chip size and increased complexity. This is the smallest possible geometry for an operating voltage up to 20 Volts.

- Each of the small transistors can either be NPN or PNP with no degradation in performance. In the NPN mode the transistor has three separate emitters and two separate bases, allowing the creation of current ratios and multiple use of a single device.

- Years of experience in the semicustom field have taught us how to design a chip which can be interconnected easily. You will find the 700 Series to be by far the easiest to route.

- All critical components, such as the resistors and small transistors have not only identical size but also identical orientation, giving the best possible matching.

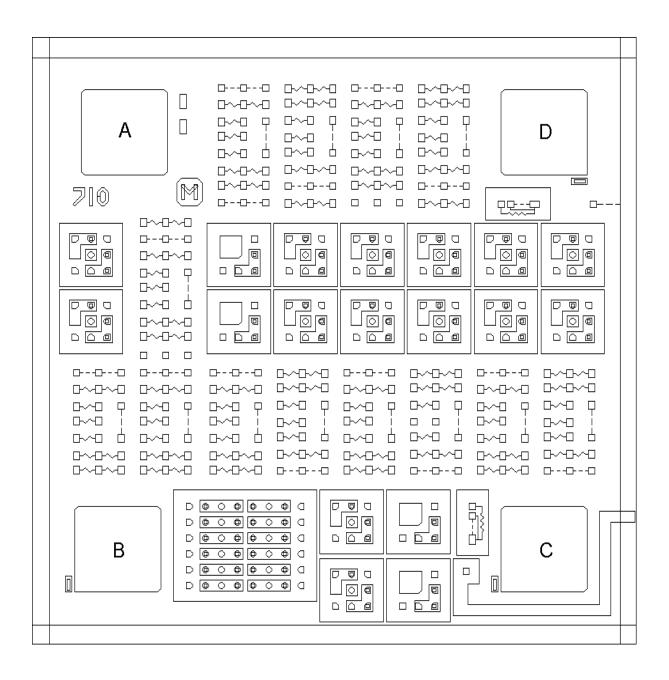

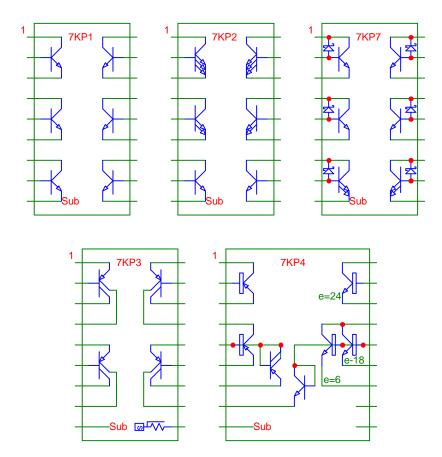

Each chip contains the same basic components and is based on an identical architecture. In the center portion of the chips are islands of 12 transistors each, 10 of which are convertible from NPN into PNP and 2 are Schottky NPN transistors. These islands are surrounded by a field of resistors. In this series the number of resistors and the total resistance is extra large, which makes it easier to design an IC, especially for first-time designers.

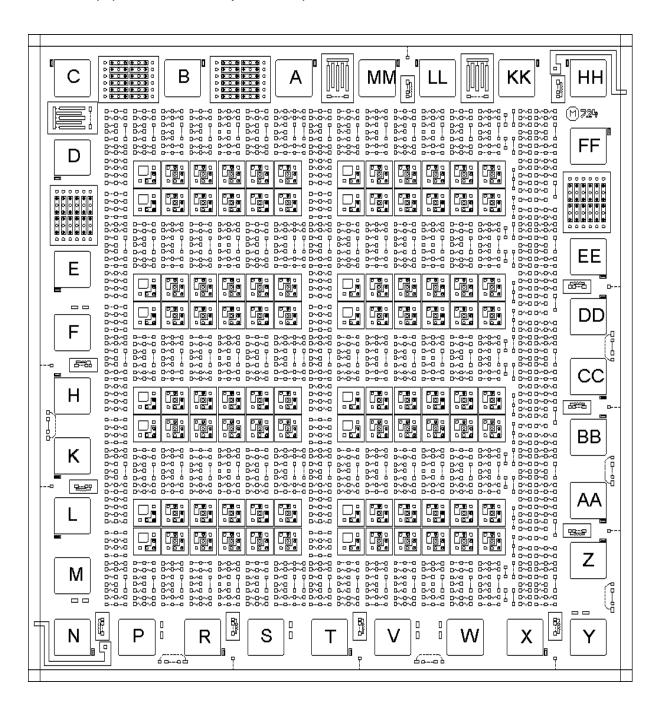

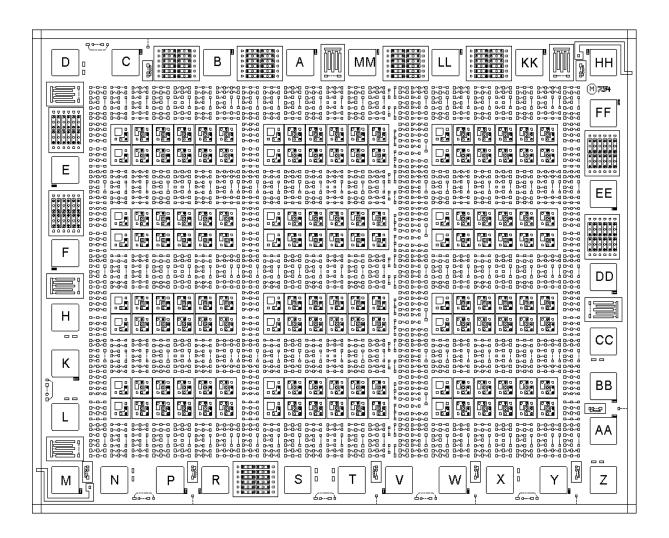

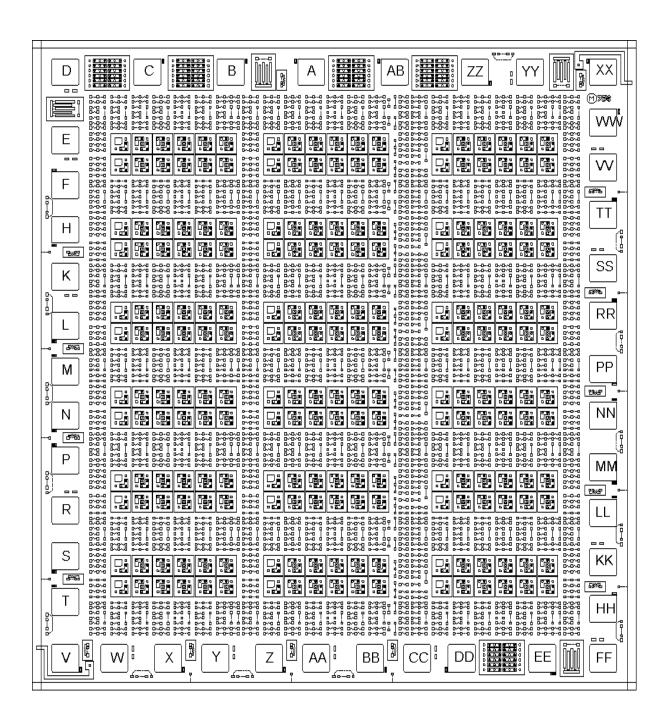

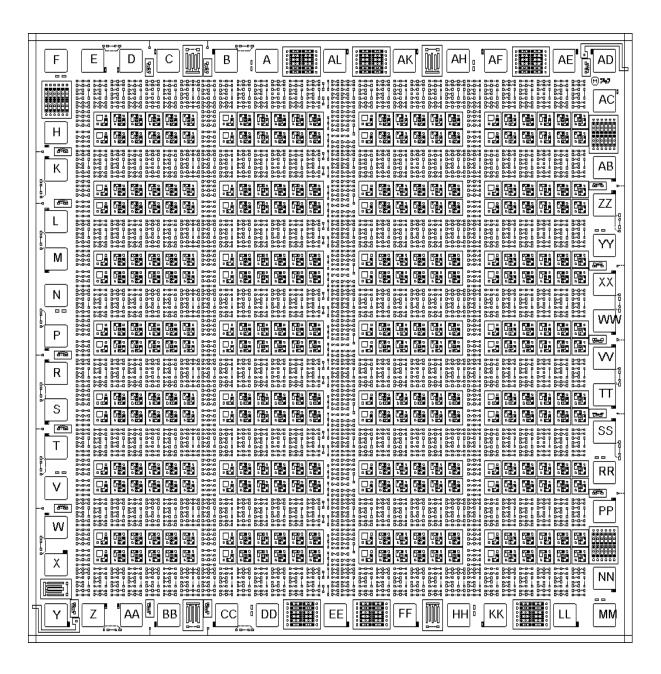

These islands of transistors are arranged in columns and rows. The *number* of the chip tells you how many columns and rows there are. The 712 chip, for example, contains a single column and two rows.

Between the bonding pads along the periphery are all other devices: large (200mA) NPN transistors, large (6mA) PNP transistors, pinch (high-value) resistors and junction capacitors. Sprinkled throughout each chip are low-value cross-under resistors.

Outside the bonding pads there is space for three interconnection lines and a wide metal stripe for the most negative potential. The positive potential can be bussed through the chip in special lanes. These two potentials automatically take care of the proper junction isolation of all the components.

# **Selecting Chip Size**

To determine the size of the chip you need consider three factors:

- 1. How many bonding pads do you need?

- 2. What is the requirement for special devices? Looming largest here is the high-current NPN transistor. Occasionally you may have to consider the higher-current PNP transistor, Schottky-clamped NPNs or capacitors.

- 3. What is the small-transistor count?

The last factor is the hardest to estimate before doing some actual design. However, you should be aware that *chip size* is not the only ingredient in the cost of an IC. There are three other factors which are equally important:

- A. The yield of a wafer (how many chips actually work) depends both on the chip size and how well the circuit is designed.

- B. To the chip cost the packaging cost has to be added. This means that a 30% increase in chip area does *not* result in a 30% increase in the cost of the assembled IC; the increase in cost is always smaller.

- C. In addition to the chip and packaging cost there is a cost associated with testing. Both a wafer test and a package test is required.

How much of a chip can you actually use? Certainly more than 70%. If you use less than 70% consider going to the next smaller chip. Because of the advanced architecture a utilization factor of 85% is not too difficult, even with a single metal layer. If you are willing to take on a bit of challenge it is quite possible to use all - 100% - of the *transistors* and you are still likely to be left with some of the resistors.

# Die Sizes / Potential (Unyielded) Die per 150mm (6") Wafer

| Die        | Size (mils)    | Die per Wafer  |  |  |  |

|------------|----------------|----------------|--|--|--|

| 710        | 22422          | 22272          |  |  |  |

| 710<br>711 | 33x33<br>44x40 | 23373<br>13695 |  |  |  |

| 712        | 47x53          | 9027           |  |  |  |

| 713        | 53x66          | 6363           |  |  |  |

| 723        | 70x66          | 4745           |  |  |  |

| 724        | 74x79          | 3703           |  |  |  |

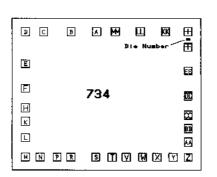

| 734        | 98x79          | 2763           |  |  |  |

| 736        | 98x105         | 2061           |  |  |  |

| 747        | 118x119        | 1480           |  |  |  |

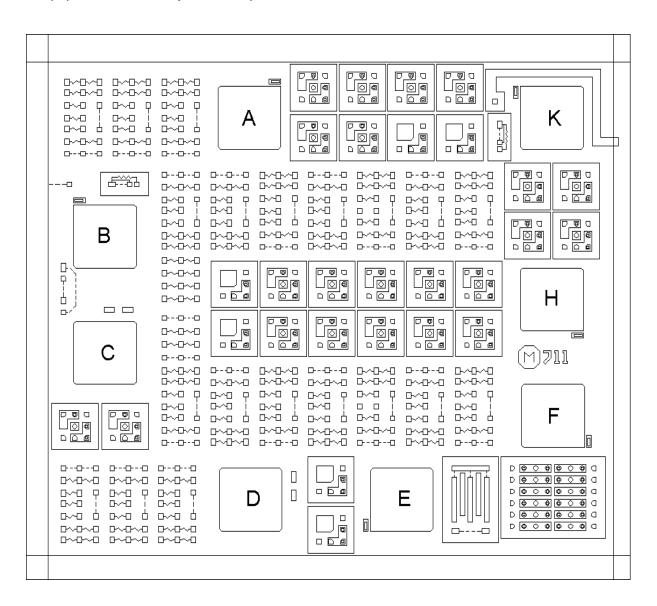

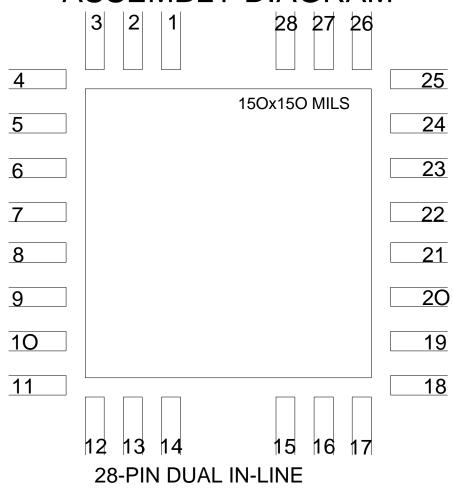

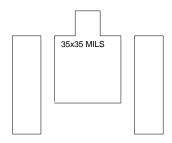

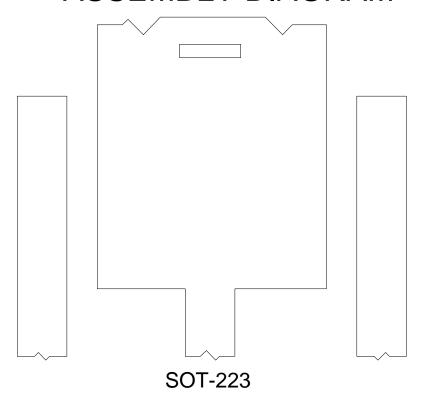

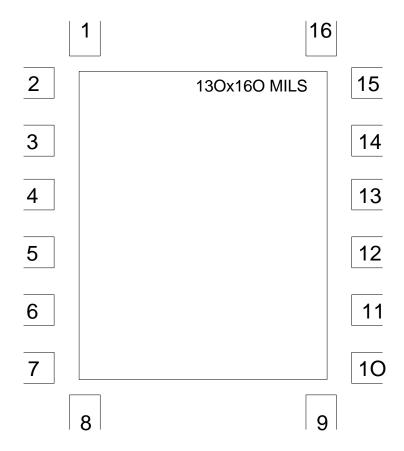

## 710 33x33 mils (0.84x0.84mm)

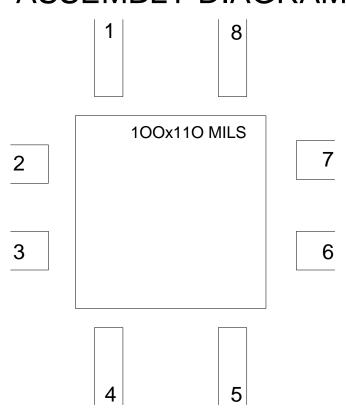

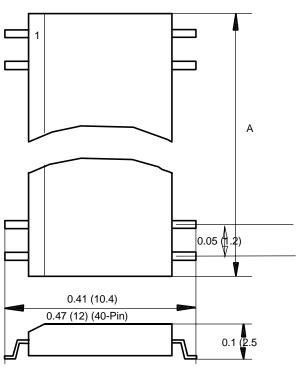

4 pads - 14 small NPN/PNP transistors - 4 small Schottky NPN transistors - 1 large NPN transistor - 91kOhms base resistance - 2 base pinch resistors - 1 epi pinch resistors - 1 junction-capacitor - 40 cross-unders - Fits smallest surface mounted packages (SOT)

## 711 44x40 mils (1.1x1mm)

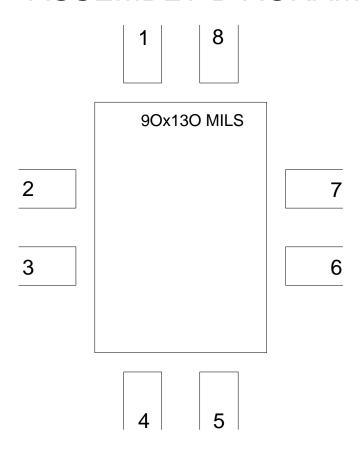

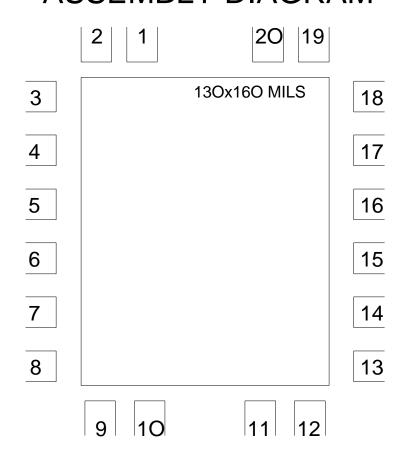

8 pads - 22 small NPN/PNP transistors - 6 small Schottky NPN transistors - 1 large NPN transistor - 1 large PNP transistor - 142kOhms base resistance - 2 base pinch resistors 1 epi pinch resistor - 2 junction-capacitors - 68 cross-unders

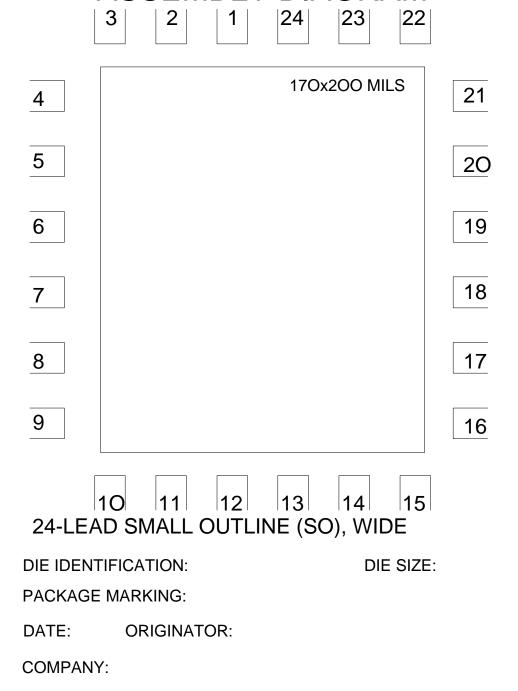

# 712 47x53 mils (1.2x1.35mm)

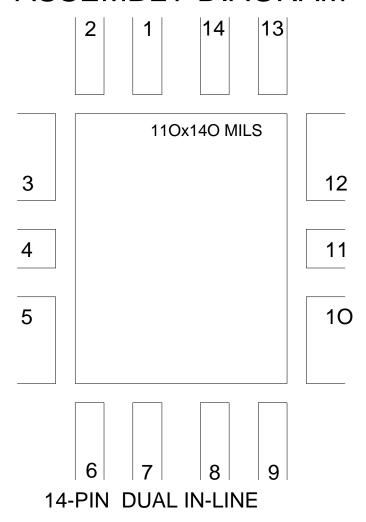

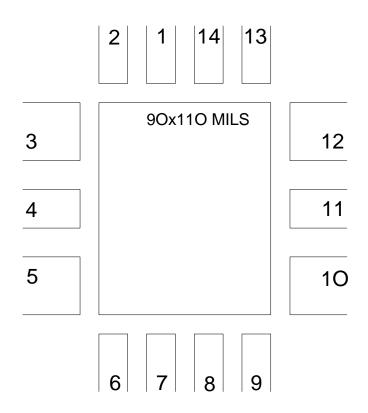

17 pads - 27 small NPN/PNP transistors - 10 small Schottky NPN transistors - 1 large NPN transistor - 1 large PNP transistor - 157kOhms base resistance - 9 base pinch resistors 2 epi pinch resistors - 2 junction capacitors - 70 cross-unders

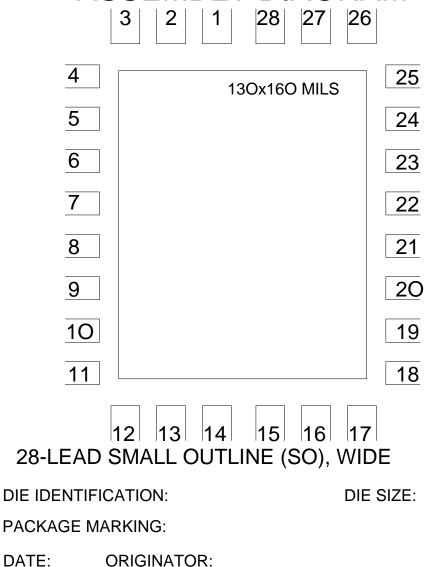

## 713 53x66 mils (1.35x1.7mm)

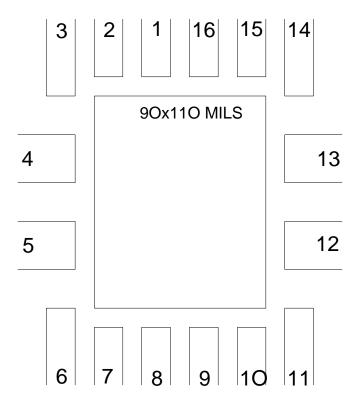

22 pads - 39 small NPN/PNP transistors - 11 small Schottky NPN transistors - 2 large NPN transistors - 2 large PNP transistors - 308kOhms base resistance - 9 base pinch resistors 2 epi pinch resistors - 4 junction capacitors - 160 cross-unders

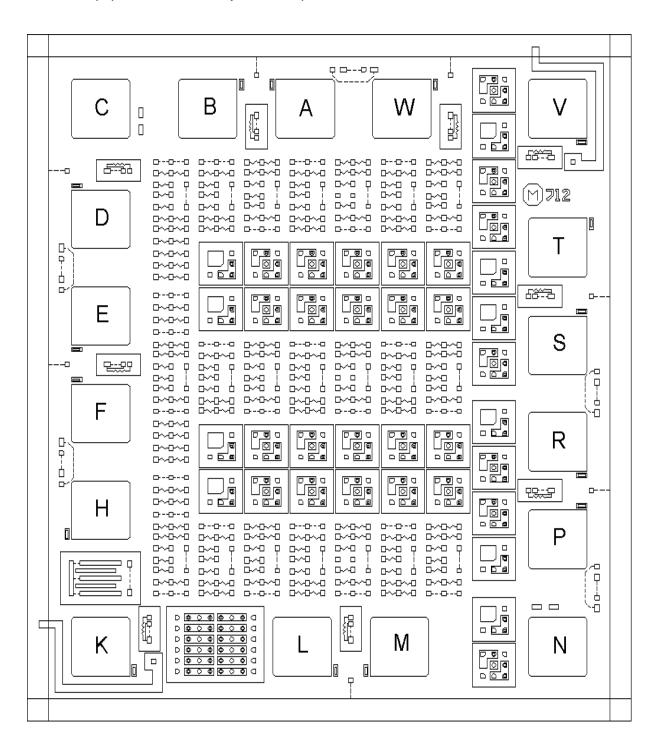

#### 723 70x66 mils (1.8x1.7mm)

25 pads - 60 small NPN/PNP transistors - 12 small Schottky NPN transistors - 3 large NPN transistors - 3 large PNP transistors - 467kOhms base resistance - 7 base pinch resistors 2 epi pinch resistors - 7 junction capacitors - 200 cross-unders

### 724 74x79 mils (1.9x2mm)

30 pads - 80 small NPN/PNP transistors - 16 small Schottky NPN transistors - 4 large NPN transistors - 3 large PNP transistors - 671kOhms base resistance - 11 base pinch resistors 2 epi pinch resistors - 7 junction capacitors - 300 cross-unders

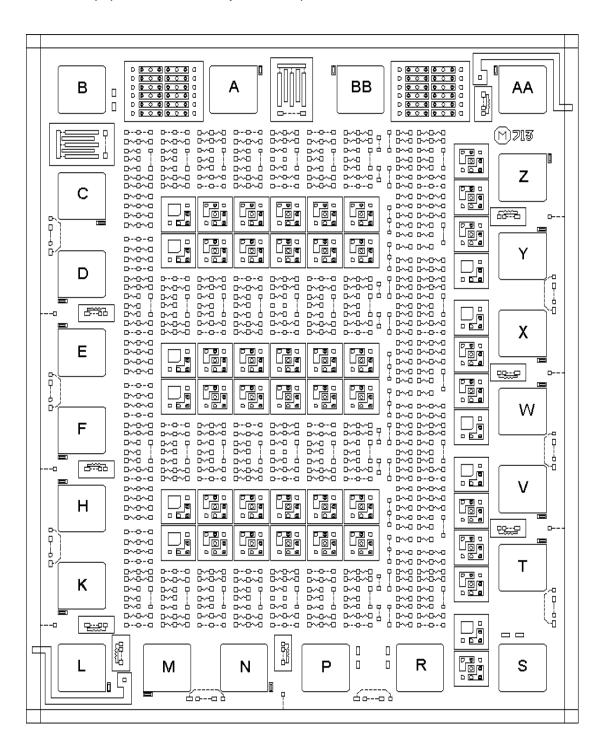

## 734 98x79 mils (2.5x2mm)

30 pads - 120 small NPN/PNP transistors - 24 small Schottky NPN transistors - 9 large NPN transistors - 6 large PNP transistors - 951kOhms base resistance - 8 base pinch resistors 2 epi pinch resistors - 9 junction capacitors - 450 cross-unders

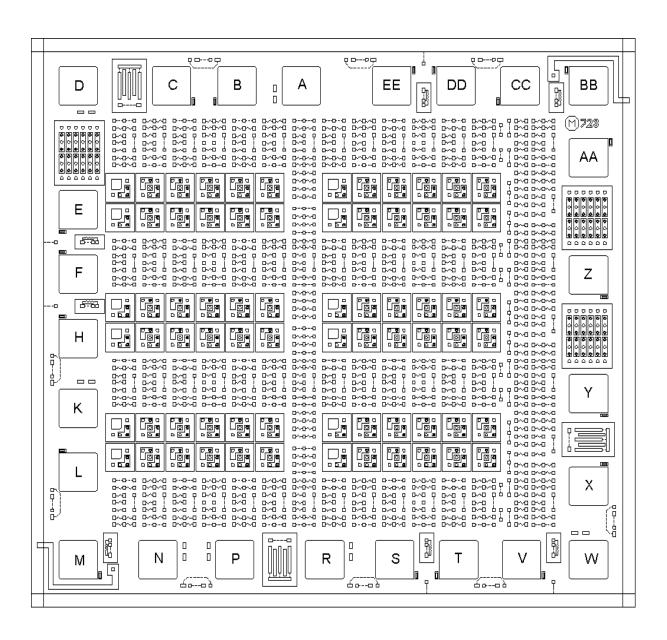

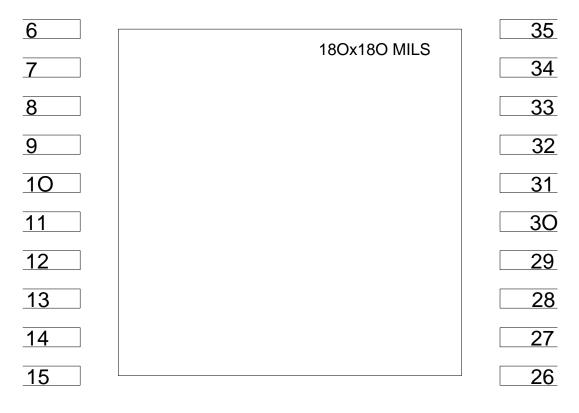

### 736 98x105 mils (2.5x2.7mm)

41 pads - 180 small NPN/PNP transistors - 36 small Schottky NPN transistors - 5 large NPN transistors - 4 large PNP transistors - 1.34MOhms base resistance -14 base pinch resistors 2 epi pinch resistors - 12 junction capacitors - 650 cross-unders

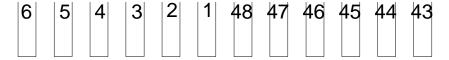

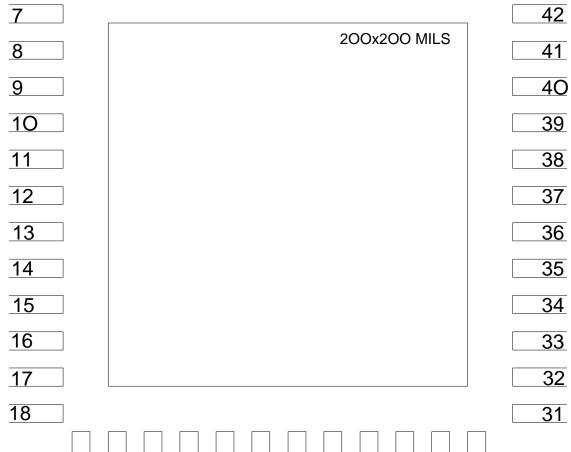

# 747 118x119 mils (3x3mm)

48 pads - 280 small NPN/PNP transistors - 56 small Schottky NPN transistors - 9 large NPN transistors - 5 large PNP transistors - 1.86MOhms base resistance - 16 base pinch resistors 2 epi pinch resistors - 10 junction capacitors - 950 cross-unders

# **Linear IC Design**

Designing linear (bipolar) integrated circuits is first of all different. Different from digital design and different from designing with discrete components and standard ICs.

There are some principles - we counted six of them. We will go through them first, slowly and carefully.

Using these design principles a lot of clever linear IC designers have come up with bits and pieces of circuits which form useful functions. If you take a close look at the schematics of some of the standard linear ICs you will recognize many of them. Even the most expert of IC designers use them. It is because of these circuit *elements* that linear IC design is manageable. You select the elements best suited for your design and connect them together so that they perform the function you desire.

That is why we have put together a large library of these linear IC design elements in the second section of this chapter, with detailed explanations and comments.

In the third section of this chapter we have collected some design examples, which we call *functions*. We intend to add to this section gradually ourselves, but most of the additions will come from the users of the 700 Series. So, if you have created a useful function or circuit, send it to us. We'll add it to the collection, with credit, of course.

All of the circuits in this chapter are contained in a zipped file. You can pull them directly into your design.

The following two books we consider the best for linear IC design:

Gray and Meyer: "Analysis and Design of Analog Integrated Circuits", John Wiley & Sons, 1984, ISBN 0-471-87493-0

Grebene: "Bipolar and MOS Analog Integrated Circuit Design", John Wiley & Sons, 1984, ISBN 0-471-08529-4

#### Part of 700 Series Manual

Copyright 1991 - 2003 Array Design Inc., San Francisco. This manual is protected by copyright law, but may be reproduced for the purpose of design or teaching. Any such reproduction must include this legal notice.

# **Design Principles**

## **Examining the Bipolar Transistor**

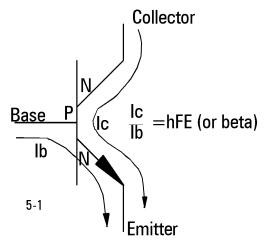

How does a transistor really work? Well, there are three layers: in the case of the NPN transistor the outer ones are p-type; sandwiched in between is a thin n-type region.

P-type means that, in the silicon crystal lattice, there are also a few atoms which have one less electron in the outermost shell than silicon (which has 4). Thus Boron, Aluminum or Gallium, which have three electrons in the last orbit, fill the bill. This makes for a *deficiency* of electrons. Since electrons have a negative charge, the resulting charge is positive, hence p-type. Likewise, the presence of atoms with 5 electrons in the outermost shell (Phosphorus, Arsenic or Antimony) causes an oversupply of electrons, i.e. the silicon becomes n-type.

These "dopant" atoms can be inserted into the silicon by diffusion (at very high temperature, which causes the dopants to penetrate even solid materials, or by ion implantation, i.e. "shooting" the atoms into the crystal lattice).

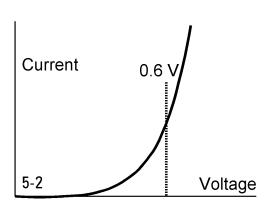

Current can flow from p to n, but only if a certain voltage (about 0.6 Volts for silicon) is exceeded (this is the conventional current flow; the electrons actually flow the other way). There is no (or very little) current-flow from n to p, except for one very important case:

If we apply a positive voltage to the base (p) and a negative one to the emitter (n) current will flow from base to emitter once about 0.6 Volts is exceeded. The electrons now flow through the thin base region. With a positive voltage applied to the collector, some of these (negatively charged) electrons are attracted by the positive collector voltage and flow toward it, rather than out the base. This flow takes place despite the fact that the collector-base junction is reverse biased; it does so solely because the base region is thin, which forces some of the electrons too close to the collector region. The thinner we make the base, the more of the electrons end up at the collector terminal rather than the base. With the base thickness used in an average

transistor (about 0.2 microns) more than 100 times as many electrons flow to the collector as do to the base. The ratio of the two we call the current gain:

hFE (or beta) = Ic/Ib

This is a (fairly) linear relationship. If we increase the base current by a factor of 10 we can expect the collector current to increase by a factor of 10 also. On the other hand, look at the base-emitter voltage. This is a forward-biased diode. Hardly any current flows below about 0.3 Volts. At about 0.6 Volts there is a substantial amount of current and at higher voltages the current increases drastically. In fact, this is an exponential relationship: at any point on the curve, an increase of about 60mV (at room temperature) causes the current to increase tenfold. If we were

to plot this curve with the current on a logarithmic scale, it would be a straight line.

The formula for a diode is:

V = kT/q ln (11/ls)

#### where

V is the diode voltage in Volts k is the Boltzman constant (1.38E-23 Joules/Kelvin) q is the electron charge (1.6E-19 Coulombs) T is the (absolute) temperature in Kelvin In is the natural logarithm

> Is is the diffusion current, which depends on the doping concentrations of the two layers, and the diode area

and I1 is the diode current

Note: 1.38E-23 is the notation for 1.38x10<sup>-23</sup>. Since it is required for Spice, we will be using this notation throughout.

At first glance one might think that the diode voltage has a positive temperature coefficient because of the presence of T. However, "Is" has a much stronger *negative* temperature coefficient, so that the overall change is about -2mV/°C

We are forced to conclude from all of this that the bipolar transistor is a good current amplifier but, as a voltage amplifier, it is very non-linear.

Let's look at another aspect of the current gain, though. As we noted above, to obtain a current gain of 100 or more, the base region must be very thin. How is this base region created? Well, first the (p-type) base region is diffused in. Then the (n-type) emitter follows and is made a little shallower. The difference between the two creates the actual base region (see chapter 2). Now, all this diffusing happens at a very high temperature, above 900°C. It needs to be this high to get the dopants to move into the silicon within a reasonable time.

At this high temperature the red-hot silicon is no longer a semiconductor. There are no diodes and there is no transistor action. So we need to let the wafer cool down before be can tell how accurate the emitter diffusion was, how much base-width we have created and what hFE has resulted.

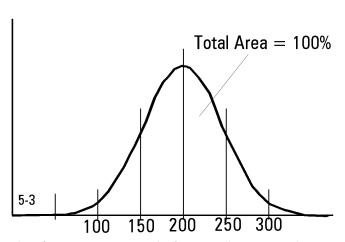

The upshot of all of this is that we cannot expect to get the same hFE every time. Sometimes we diffuse a little too deep, sometimes a little too shallow. Summing it up in one sentence: we get a distribution. Shown here is the Gaussian distribution, where the total number of measurements is represented by the area under the curve. Most wafers will show an hFE around 200, but some will be 100, some 300. Since individual transistors on a wafer are not accessible (and we couldn't do much to change the hFE anyway), we are forced to design a

circuit so that is works well with an hFE ranging from 100 to 300. In fact, as the curve shows, even this does not include *all* transistors; a small (hopefully very small) percentage will have an hFE beyond the limits.

Not all distributions are Gaussian. The current gain distribution, for example, is slightly asymmetrical. But it is usually accurate enough to assume that we are dealing with a Gaussian distribution only.

For the Gaussian distribution it is handy to use sigma deviations. A deviation (from the average, or peak of the curve) of one sigma (in both directions) includes 68% of all measured values. Twice that deviation (2 sigma) includes 95% and 3-sigma 99.7%. Thus, if we give a 3-sigma range of hFE (for the NPN transistor) of 100 to 300, 0.3% of the transistors may have a current gain outside this range. If you cannot live with a larger range you will need to eliminate the 0.3% through testing. More on statistical distributions in chapters 3 and 10.

This is a fact of life in ICs and applies to all devices and almost all parameters. Consider, for example the resistor. There are three semiconductor layers in the 700 series which could be used as resistors: the epitaxial layer, the base diffusion and the emitter diffusion. Their resistance depends on how heavily the region is doped - the more dopant atoms (either p or n) the lower the resistance. The base diffusion gives the most practical range of resistance and is, therefore, almost universally used.

We can delineate (with a mask) a strip of base diffusion, place contacts at either end and we have a resistor. If we make the strip long and narrow, the resistance will be high; short and wide gives a low resistance value. This part is simple; what's not so simple is that the base diffusion wasn't really made to be a resistor. First of all, it is a semiconductor material and as such doesn't have the best properties for a resistor; its temperature coefficient, for

example, is considerably higher than that of a metal-film resistor. Second, the NPN transistor has first call on the properties of the base layer. Third, as with the hFE, we cannot measure the resistance while it is being made. At the high diffusion temperature the base layer no longer even resembles a semiconductor.

So, again, there are variations. About  $\pm 25\%$  (3-sigma), to be specific, much more than even the least expensive carbon resistor. And, of course, unlike the carbon resistor, we cannot test each resistor and put it in separate bins according to value. Nor can we trim it like a metal-film resistor.

But there is a hidden advantage, which has become one of the most powerful design tool in linear IC design. While the resistors (and hFEs and most other parameters) may vary a great deal from wafer to wafer, they are likely to be the same on a wafer. We may miss the target but, if we do, it will affect all devices on a wafer by (very nearly) the same amount. This leads us to the first design principle:

# **Principle #1: Use Matching**

While the absolute variation of almost all parameters in an IC is large, their relative values tend to be close together because they have undergone the same treatment and are in close proximity.

For example, (base diffused) resistors have a (3-sigma) variation of ±25%, but their *ratios* vary by only 2% (3-sigma), even less if you use many of them together. Thus, you can count on two equal values to be very nearly the same, not matter what they may be. Furthermore, you can create quite accurate *resistor ratios other than 1*. In a full-

custom IC this is normally done by giving two resistors different lengths; in the 700 Series you do it by connecting identical resistors in series or parallel (which results in the best possible matching accuracy).

But matching goes far beyond the resistor. All transistor parameters (most importantly their hFEs and VBEs) match well. This property, as you will see soon, leads to the ubiquitous differential pair.

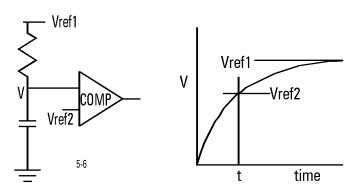

To illustrate this principle, we are going to analyze an example: the 555 timer. Before its appearance, a timing function was generally designed as shown on the right. A capacitor is charged through a resistor from a (regulated) reference voltage Vref1. The voltage across the capacitor is sensed by a comparator. When this voltage reaches the level of a second (regulated) reference voltage Vref2

(somewhat lower that Vref1), the comparator switches. It's not a very elaborate circuit, except that we need two accurate reference voltages; both of them influence the timing.

Enter the principle of matching. We throw away both reference voltages and use a string of matched resistors to create Vref2. At first glance you might think that we have a much less accurate circuit now. But observe that, with three equal resistors, the trigger point is 2/3 of the supply voltage; the only tolerance here is determined by the matching accuracy of the three resistors. Now increase the supply voltage: the trigger point increases proportionally, but so does the charging current. The two effect cancel precisely. If the input current of the comparator is small and the matching accurate, the time is only a function of the external capacitor and resistor. We have eliminated the need for absolute accuracy within the IC.

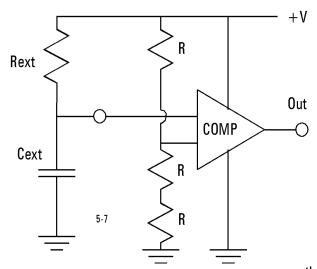

Let's extend this principle to the transistor. An example that is easy to grasp is the comparator. When one input moves past the other, its output switches. For a well-designed comparator, this happens within a few millivolts. With single transistors this would be very difficult to achieve; with pairs it is a simple task.

Our comparator example here is still very primitive, using only the first of the

linear design principles. A pair of NPN transistors share the same resistor, RB. With the two inputs at the same voltage, the current flowing through RB splits evenly between the two transistors. Thus one-half the total current flows through RL, creating a voltage drop at the output. Notice that, so far, there was no need to talk about transistor parameters. No matter what they are, the current will split into two equal parts, as long as the transistors match.

Now increase the right-hand input. Through the base-emitter diode you force its emitter to a higher voltage. Therefore, it takes a larger share of RB's current and the output voltage drops. If you decrease the right-hand input, the opposite happens.

Because the base-emitter diode has an exponential voltage-current characteristic, this switching of currents from one side to the other happens gradually, over a range of a few hundred millivolts. So, what we have here is a rather poor comparator, one with a soft threshold. In other words: the comparator has very little gain.

# **Principle #2: Replace Resistors with Current Sources**

There is also something else wrong with this design: As we increase the higher of the two inputs, the voltage drop across RB increases by nearly the same amount (the input voltage minus the diode drop). Thus the total current is set by the higher of the two input voltages and varies a great deal.

Let's tackle this second problem first. Why is there a resistor used to deliver the current to the emitters of the differential pair? Part of it is tradition. A resistor is the least expensive discrete component. For an IC, it might well be the most expensive component, especially if is needs to be a large value and thus take up a lot of IC area. Also, it is the *wrong* component.

What we really want is a *current source*, a device which delivers a current independent of voltage (Actually, the proper term here is current *sink*, but it has become common practice to call all these elements current sources, regardless of their actual position.) There are no discrete components which are, by themselves, current sources, but in an IC we can make one, usually taking up less area than an equivalent resistor.

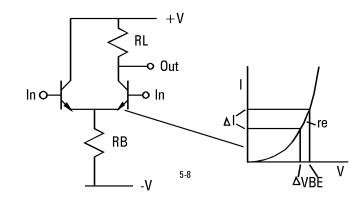

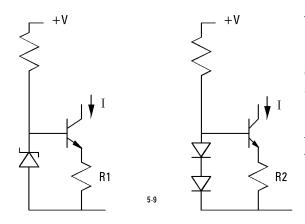

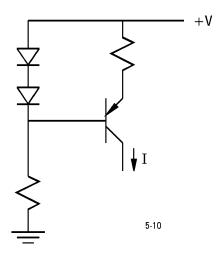

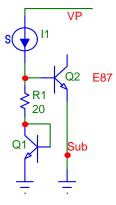

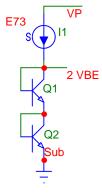

There are two designs shown here (more - many more - later in this chapter). The one on the left uses a Zener diode to set up a voltage at the base of a transistor. The current through the transistor is simply given by the Zener voltage (say 6 Volts), minus the base-emitter voltage, divided by R1. Now, as long as the collector voltage is a bit higher than that of the emitter, the transistor current is fixed. Disadvantage: you need some extra voltage room.

The current source on the right has a slightly poorer performance, but it doesn't waste much supply voltage. Here the base voltage is set by two diodes (about 1.3 Volts). From base to emitter we drop one diode voltage, so the voltage across R2 is one diode voltage. Again, the current through the transistor is this voltage divided by R2 and the collector voltage can drop to about one diode drop above the minus supply. Since diodes (in the forward direction) are exponential devices (i.e. not nearly as sharp as a Zener diode), the current is a bit dependent on the supply voltage.

The previous two examples are current sinks. You can make an equivalent current source with a PNP transistor.

If, for example, we wanted to create a current of 50 microamperes, the required resistor value would be approx:

R = Diode Voltage(VBE) / I = 650mV / 50uA =13kOhms

The equivalent discrete resistor with a 10 Volt supply would be 200kOhm, which would require an area many times that of this current source.

Lets go back to our comparator. In the next figure we replace both resistors with current sources.

The one at the bottom provides the operating current for the differential pair, which now changes very little as the inputs are moved up and down. The one at the top replaces the load resistor; since its impedance is very much higher than that of a resistor, we now get a large amount of gain.

The impedance of an ideal current source is infinite. In most practical current sources the current always increases somewhat with increasing voltage. But the resulting impedance (i.e. slope) ranges from hundreds of kilo-Ohms to a hundred Meg-Ohms, an increase of 100 to 10000 compared to a simple resistor.

The voltage gain of a transistor stage is roughly given by the load impedance divided by the impedance in the emitter. The latter is the slope of the base-emitter diode, roughly 26 Ohms/mA at room temperature (more on this under differential stages). If a transistor is operated at say 100uA, the emitter resistance is 260 Ohms. With a load impedance of 1MOhm, the resultant voltage gain is about 3800. Using a resistor as load (say 40kOhms, allowing a 2 Volt DC drop), the voltage gain is only 154. Besides that, three transistors and one low-value resistor take up much less area than one 40kOhm resistor.

But there is still one problem with our comparator. To work as designed, the load current must be exactly one-half of the operating current. We can come close, but there is a better way:

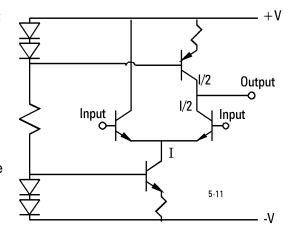

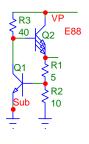

Study the picture on the right carefully, you are going to see it (and numerous derivatives of it) many times in linear IC design.

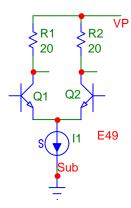

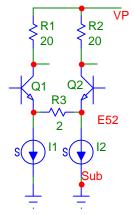

First note that the transistor on the left has its base connected to the collector, i.e. it is connected as a diode. Its collector voltage is controlled by the base, which has the already mentioned exponential (and very accurate) voltage-current characteristic. There is still transistor action though - the collector voltage is well above saturation - and Ic is hFE times larger than Ib.

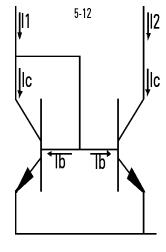

Now the transistor on the right. Its base and emitter are connected to the same terminals as that of the first transistor. Therefore, it must draw the same base current. Since the two devices match, they also must have the same hFE. Therefore, the two collector currents are the same and I1=I2. We have *mirrored* I1.

Well, not quite. There are two errors which make this current mirror a bit less than ideal. The first one: both base currents are supplied by I1. Thus the collector current of the left-hand transistor is I1-2lb, and it is this current that is mirrored. With an hFE of 100, I2 is 2% smaller than I1.

The second error is more serious. As the curves in chapter 3 show, hFE is voltage dependent. This "Early effect" arises from the fact that each junction has a region where the electrons and holes are separated by the voltage (the "space charge region"). As the voltage is increased this region widens and is pushed further into the thin base region. This decreases the base-width, thus increasing the gain.

The upshot of this long-winded explanation is that, the higher the voltage of I2, the more it will increase over I1. This error can amount to as much as +20%. Much more on this under current mirrors later in this chapter.

Exactly the same configuration is possible with a PNP transistor. Here we have a further advantage. As shown in chapter 3, in a (lateral) PNP transistor the collector can easily be split into segments. In the 700 Series the PNP transistors come with two identical collector halves. Thus a single device can be connected as a complete 1:1 current mirror.

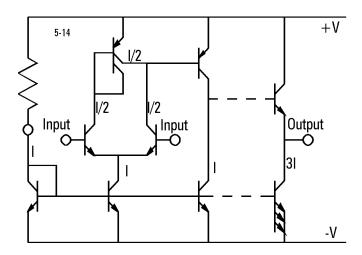

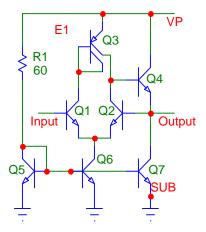

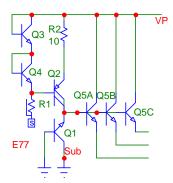

Now back to our comparator, and this time the design is complete. We have employed a PNP current mirror as the load of the differential stage. Now even if the operating current I varies, one-half of it will be mirrored.

Notice the four transistors at the bottom. The left-most transistor is diode-connected, steering a total of *three* other transistors: the first delivers the operating current to the differential pair, the second forms a load for the second stage (more high gain) and the third supplies the bias

current for the output stage. Since the output stage normally requires more current (to drive loads), we have simply given that transistor 3 emitters, so that it draws three times the base current and delivers 3I. In the 700 Series the NPN transistors can have one, two or three emitters, just for that purpose.

# **Principle #3: Current Amplification**

As we have noted above, the voltage gain in the bipolar transistor is anything but linear. Current gain (hFE), on the other hand, is a naturally linear parameter. For this reason alone it is easier to achieve high performance stressing current rather than voltage amplification.

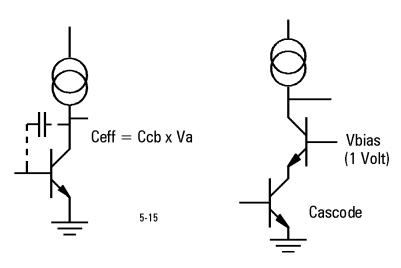

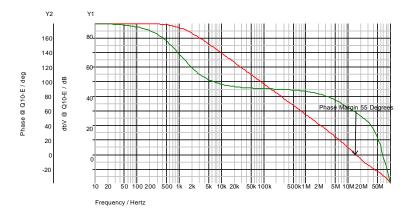

But there is a second reason. Each junction has a capacitance (created by the "space-charge region"). Of particular bother is the collector-base capacitance. Not that it is especially large (it isn't), but it is badly situated. Using the transistor as a voltage amplifier, base and collector terminals move in opposite directions (i.e. they are 180° out of phase). Since the transistor is capable of a large voltage gain (especially with a current source load), the voltage swing at the collector can be several hundred to several

thousand times as large as that of the base. Looking into the base, the far end of the collector-base capacitance has a large voltage swing, and thus its capacitance appears to be far larger. This "Miller effect", simply put, *multiplies* the C-B capacitance by the voltage gain. So, if the junction capacitance is say 0.5pF and the voltage gain 1000, a 500pF capacitance is presented to the input. With an input impedance of 10kOhms, the cutoff frequency is a mere 32kHz, a far cry from the real capability of the transistor.

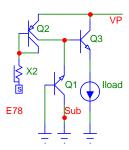

The quick fix to this problem is the so-called Cascode stage. An additional transistor, with its base connected to a fixed bias voltage just high enough to keep the first transistor out of saturation, shields the input. The Miller capacitance now works against the bias voltage which, presumably, has a low impedance.

The cascode stage is only a halfhearted use of current amplification. A better approach (at least for high-frequency performance) would be to avoid converting to a voltage altogether.

# Principle #4: Delta VBE

As we have seen above, the forward conduction of a diode is an exponential curve. Its absolute magnitude of the voltage contains the expression:

where In is the natural logarithm, I1 is the current at which you are measuring the voltage and It is the saturation current. This latter parameter is a problem; apart from the material (silicon) it depends on the doping levels of both sides of the junction and the area of the diode. Thus, an NPN transistor connected as a diode, for example, has a different *absolute* forward characteristic compared to a PNP transistor.

However, if we forget about the absolute level and concentrate on relative levels, we find that the manufacturing parameters drop out completely. The beauty of an exponential curve is its constant slope for ratios. If we start at a very low current and increase the current by say a factor of 10, we find that the voltage changes by a certain amount. If we now move to a much higher current and change it again by

a factor of 10, we get exactly the same voltage change. The expression for this is:

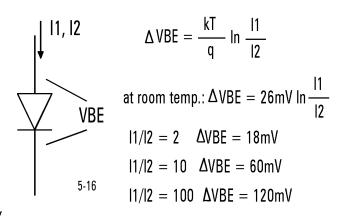

Delta-VBE =

$$(kT/q) \ln (11/l2)$$

The term VBE is commonly used in bipolar IC design for the diode voltage. It signifies the voltage between base and emitter, the most practical diode junction in an IC. All of the diodes we are discussing here are in fact transistors. By far the best connection consists of tying base and collector together. Since the current through the base in this connection is only 1/hFE of the total current (the major portion flows through the collector), the resistance of the base plays only a minor role (the collector resistance is not factor at all until the current is so high that the transistor saturates). The exponential behavior of such a diode-connected transistor is very accurate over about 8 decades of current.

At room temperature kT/q is approx. 26mV (a handy value to remember).

There is a second part to this formula: The change in voltage (delta VBE) can be created by changing either the current (as we have done so far) or the *area*. If we double the area of the diode, its voltage will drop 18mV at room temperature (at any current). If we increase it by a factor of 10, the drop is 60mV. What is important here is the *current density*, i.e., for example, milliamperes per square centimeter of diode area, but only in a relative way. It is never necessary for us to know the actual area of the diode.

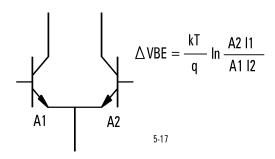

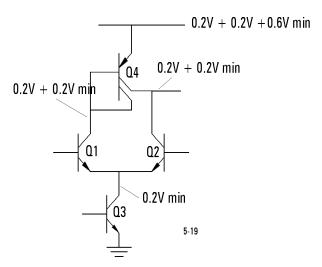

The complete formula is shown in this figure, applied to a differential pair. If we double A2, for example (connect two emitters), we drop its base-emitter voltage by 18mV. In this way we can create a precise offset voltage. However, notice that this delta VBE is *proportional to absolute temperature*. If 18mV is our choice at room temperature, we get 24mV at 125°C and 13.2mV at -55°C. How do you counteract that? Make the current proportional to absolute temperature too.

So, we can create a delta-VBE with a current ratio or an area ratio, or both at the same time.

Delta-VBE is one of those parameters that comes along once in a generation. It is not affected by the process and it is highly predictable over a very wide range of current. True, it is dependent on temperature, but that again can be turned into a significant advantage, as we shall see next.

## Principle #5: Delta-VBE vs VBE

Delta-VBE has a positive temperature coefficient. It is not just *some* positive temperature coefficient; it is strictly related to absolute temperature. At zero Kelvin delta-VBE is zero and increases from there in a straight line.

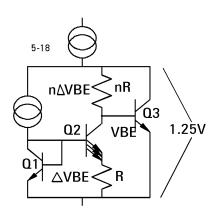

We have also noticed, casually, that VBE has a negative temperature coefficient. As it happens, this temperature coefficient is not just some arbitrary number either. As we lower the temperature, VBE increases linearly until it reaches a very specific voltage at absolute zero. For silicon this voltage is 1.25 Volts, the bandgap voltage, which tells us how much voltage does it take for electrons to cross the energy gap. This is a fundamental atomic constant and it not dependent on the process.

So, if we take a VBE and add it to a voltage related to delta-VBE we get less of a temperature coefficient. In fact, if we add enough delta-VBE voltage to the VBE, the two temperature coefficients cancel. The total voltage at which this happens is - surprise - 1.25 Volts, the bandgap voltage.